Circuit Descriptions, Abbreviation List, and IC Data Sheets

8

7

9.

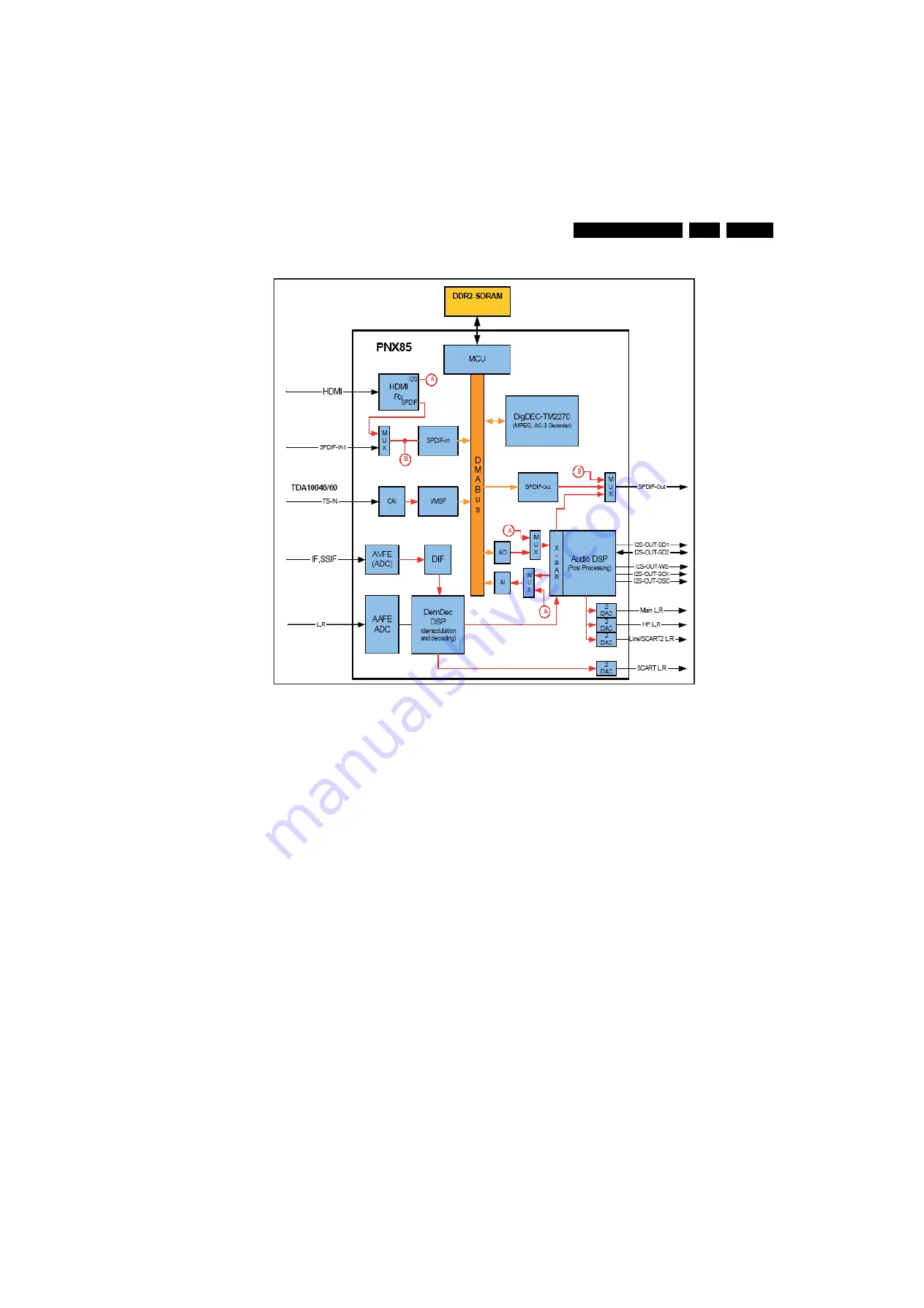

Figure 9-9 PNX

8

5xx audio flow diagram

The Analogue Audio Front-End Input (AAFE) block is used to

capture Baseband Audio Inputs.

The Sony/Philips Digital Interface (SPDIF) input is used to get

compressed data into the system memory. The multiplexer in

front of the block allows two possible sources of SPDIF signals.

The SPDIF Output is used to generate either PCM data or a

compliant IEC-61937 compressed stream containing

MPEG/Dolby Digital format.

The Audio Input (AI) block is used to transfer stereo audio (I

2

S

channel) from the Audio DSP into the system memory for “lip-

sync” delay.

The Audio Output (AO) block supports output of up to four

stereo I

2

S channels. The AO is used to transfer data from the

system memory to the Audio DSP, for post processing of the

signal at a sampling frequency of 48 kHz (max.).

Demodulation & Decoding DSP is used for demodulation and

decoding of all analogue terrestrial TV sound standards that

the TV520 platform covers.

The Audio Post-Processing DSP supports DPLII together with

volume and tone control, spatializers, and equalizers for 6

channels (max.)

Digital Audio Decoder DSP is used to decode digital

compressed streams such as MPEG and AC-3. This runs as

SW Codecs on the AV-DSP.

9.6.3

Audio-Video Codec Subsystem

The AV Codec subsystem consists of the modules required to

capture and de-scramble Transport stream inputs together with

decoding of Audio/video Streams. Refer to figure “PNX85xx

video flow diagram” for a clarification.

The sub-system consists of the following modules:

The Conditional Access Interface block provides a direct

interface towards a PCMCIA socket for Conditional Access. It

supports both the DVB CI-CA Specification and the CableCard

(POD) Interface.

The MPEG System Processor (VMSP) provides parsing an

MPEG-2 transport stream, including de-scrambling, de-

multiplexing and appropriate routing of data to the memory.

The Video MPEG Decoder (VMPG) performs MPEG2

decoding for both MP@ML and MP@HL streams.

9.6.4

Control and Compute Subsystem

Refer to figure “Control and compute subsystem” for a

clarification of the blocks that are used in this device.

H_16770_125.ep

s

1

3

0707

xx