46

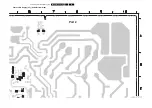

BJ2.4U/BJ2.5U LA

6.

Block Diagrams, Test Point Overviews, and Waveforms

Block Diagram Video

1020

1030

AV1-AV6_FBL-HSYNC

AV6_VSYNC

AV7_Y-CVBS

1

5

2

4

3

1070

AV7_C

AV1-AV5-AV6_G-Y

AV1-AV5-AV6_B-PB

AV1-AV5-AV6_R-PR

7012

7011

7010

+8V

1

5

2

4

3

1080

AV2_C

AV2_Y-CVBS

BE2

BE2

BE2

BE2

BE2

BE2

BE2

BE2

BE2

1060

1050

AV2-AV4_G-Y

AV2-AV4_B-PB

AV2-AV4_R-PR

7002

7001

7000

+8V

BE2

BE2

BE2

AV2-AV4_G-Y

AV2-AV4_B-PB

AV2-AV4_R-PR

B6B

PACIFIC3: PART2

B3G

MPIF MAIN: CONNECTIONS B

B3B

VIDEO

B6B

PACIFIC3: PART2

B4G

PNX2015: DISPLAY INTERFACE

B5B

VIPER: MAIN MEMORY

B5

VIPER:

B5B

VIPER: MAIN MEMORY

B4

PNX2015:

B3

MPIF MAIN:

B2B

MAIN TUNER + OOB TUNER

B2A

CHANNEL

DECODER

B10C

BUFFERING

B10A

POD

B10B

D

SIDE I/O

BE1

EXTERNALS A

BE2

EXTERNALS B

B3F

MPIF MAIN: CONNECTION A

B7A

HDMI

B7B

HDMI: I/O + CONTROL

1001

P

M

A

L

C

A

D

A

D

A

D

U

V

P

M

A

L

C

A

D

+

CVBS-IF

123

CVBS1

126

CVBS2

1

CVBS_DTV

12

CVBS|Y3

4

C3

5

CVBS|Y4

8

C4

9

Y_COMB

15

C_COMB

16

R|PR|V_1

25

G|Y|Y_1

26

B|PB|U_1

27

R|PR|V_2

30

G|Y|Y_2

31

B|PB|U_2

32

YUV

RGB

CLAMP

LPF

LEVEL

ADAPT

INV.

PAL

DATA

LINK

3

DATA

LINK

2

STROBE1N 60

STROBE1P 61

DATA1N 62

DATA1P 63

50

51

52

53

55

56

57

123

2nd

SIF

A/D

CVBS-OUTB

CVBS SEC

LPF

LPF

CVBS-OUTA

Yyuv

2FH

C-PRIM

CVBS/Y RIM

Yyuv

1T04

TD1336O

MAIN HYBRID

TUNER

2

7

8

1C52

SIFINP

SIFINN

VIFINP

VIFINN

12

CVBSOUTIF-MAIN

AV1_CVBS

AV2_Y-CVBS

AV2_C

FRONT_Y-CVBS

FRONT_C

AV7_Y-CVBS

AV7_C

AV1-AV5-AV6_R-PR

AV1-AV5-AV6_G-Y

AV1-AV5-AV6_B-PB

AV2-AV4_R-PR

AV2-AV4_G-Y

AV2-AV4_B-PB

R4

R3

R2

R1

P4

P3

P2

P1

N4

N3

N2

N1

AVP1_DLK1SN

AVP1_DLK1SP

AVP1_DLK1DN

AVP1_DLK1DP

AVP1_DLK3SN

AVP1_DLK3SP

AVP1_DLK3DN

AVP1_DLK3DP

AVP1_DLK2SN

AVP1_DLK2SP

AVP1_DLK2DN

AVP1_DLK2DP

STROBE3N

STROBE3P

DATA3N

DATA3P

STROBE2N

STROBE2P

DATA2N

DATA2P

7J00

PNX2015E

B3f

B3f

B3f

B3f

B3f

B2f

B3f

B7a

B7a

B7a

B3f

B3f

99

100

107

108

EF

7C56-2

EF

7C56-1

120

CVBS-TER-OUT

N.C.

B3f

MPIF

+5VMPIF

14

28

35

SUPPLY

46

SDA-DMA-BUS2

40

SCL-DMA-BUS2

DIGITAL

BLOCK

Yyuv

2Fh

U,V

MONO SEC.

TIMING

CIRCUIT

46

M3

CLK-MPIF

40

M4

HV-PRM-MAIN

CLP PRIM

CLP SEC

CLP yuv

SOUND

BPF

LPF

LPF

TRAP

GROUP

DELAY

QSS

QSSOUT

AUDIO SWITCH

TO AM INTERNAL

LPF

CVBSOUTIF

IF

SOURCE SELECTION

7C00

PNX3000HL

DATA

LINK

1

19

22

N.C.

N.C.

G_15930_066.eps

130606

1

7

8

1T41

14

7T41

UPC3218GV

AGC COTROL

AUX-IF-AGC-MAIN

3

2

14

15

6

7

out

in

TUNERA

GC-MON

F

A

T

-IF-A

GC-MAIN

52

50

5

13

FAT-ADC-INN-MAIN

FAT-ADC-INP-MAIN

9

10

7TG0

NXT2003

FS-OUTN

FS-OUTP

FDC-ADC-INN

FDC-ADC-INP

35

36

28

29

CATV

OUT OF BAND

TUNER

7T43

UPC3220GR

5

6

10

9

15

16

12

13

IF-TER2

53

3C73

3C71

1

4

2

5

FE-DATA

STROBE1N-MAIN

STROBE1P-MAIN

DATA1N-MAIN

DATA1P-MAIN

STROBE3N-MAIN

STROBE3P-MAIN

DATA3N-MAIN

DATA3P-MAIN

STROBE2N-MAIN

STROBE2P-MAIN

DATA2N-MAIN

DATA2P-MAIN

AVP1_HVINFO1

MPIF_CLK

D

A

T

A

LINK 1

D

A

T

A

LINK 3

D

A

T

A

LINK 2

7B11

TDA9975

19

1

18

2

1

1B01

3

4

7

9

10

12

15

6

16

19

1B33

ARX2+

ARX2-

ARX1+

ARX1-

ARX0+

ARX0-

ARXC+

ARXC-

ARX-DCC-SCL

ARX-DCC-SDA

ARX-HOTPLUG

1B32

1B31

1B30

PARX2+

PARX2-

PARX1+

PARX1-

PARX0+

PARX0-

PARXC+

PARXC-

HDMI

CONNECTOR

19

1

18

2

1

1B02

3

4

7

9

10

12

15

6

16

19

1B33

BRX2+

BRX2-

BRX1+

BRX1-

BRX0+

BRX0-

BRXC+

BRXC-

BRX-DCC-SCL

BRX-DCC-SDA

BRX-HOTPLUG

1B32

1B31

1B30

PBRX2+

PBRX2-

PBRX1+

PBRX1-

PBRX0+

PBRX0-

PBRXC+

PBRXC-

HDMI

CONNECTOR

HDMI

RX2+A

RX2-A

RX1+A

RX1-A

RX0+A

RX0-A

RXC+A

RXC-1

RX2+B

RX2-B

RX1+B

RX2-B

RX0+B

RX0-B

RXC+B

RXC-B

SDA-MM-BUS1

SCL-MM-BUS1

DV4-DATA

DV5-DATA

DV4-CLK

DV-HREF

DV-VREF

DV-FREF

D1

A2

A1

C2

L16

L15

BRX-DCC-SCL

BRX-DCC-SDA

HSCL B

HSDA B

AV1-AV6_FBL-HSYNC

AV6_VSYNC

AV2-AV4_G-Y

AV1-AV5-AV6_G-Y

AV2-AV4_R-PR

AV1-AV5-AV6_R-PR

AV2-AV4_G-Y

AV1-AV5-AV6_G-Y

AV2-AV4_B-PB

AV1-AV5-AV6_B-PB

AV2-AV4_R-PR

1

AV2-AV4_G-Y

2

AV2-AV4_B_PB

3

AV2-FBL

4

AV2_C

6

AV2_Y-CVBS

7

10

11

12

C-MON-OUT

22

AV7_C

AV2-STATUS

23

1E40

1E40

Y-CVBS-MON-OUT

9

AV6_VSYNC

REGIMBEAU-AV6-VSYNC

AV7_Y-CVBS

AV1_CVBS-AV7-Y-CVBS

AV1-STATUS-AV7-C

25

CVBS-TER-OUT

33

FRONT_Y-CVBS

34

FRONT_C

1

2

3

5

1E62

1E62

1

2

3

5

AV1-AV5-AV6_R-PR

AV1-AV5-AV6_G-Y

AV1-AV5-AV6_B-PB

AV1-AV6_FBL-HSYNC

6

6

AV6_VSYNC

N.C.

N.C.

N.C.

N.C.

N.C.

AV1-AV5-AV6_R-PR

AV1-AV5-AV6_G-Y

AV1-AV5-AV6_B-PB

AV1-AV6_FBL-HSYNC

FRONT_Y-CVBS

FRONT_C

AV2_C

AV2_Y-CVBS

Y-CVBS-MON-OUT

AV6_VSYNC

AV7_Y-CVBS

AV7_C

2

4

1M36

1M36

2

4

FRONT_C

FRONT_Y-CVBS

1

5

S VIDEO

2

4

3

1002

C

Y/CVBS

C

Y

COMMON

INTERFACE

HARDWARE

CONTROLLER

7P03

STV0701

POD

1P01

DV4_DATA_0 T0 9

DV5_DATA_0 T0 9

DV1F-DATA 0 TO 7

DV2A-DATA 0 TO 7

DV3F-DATA 0 TO 7

7V00

PNX8550

DV-ROUT(0-9)

DV-GOUT(0-9)

DV-BOUT(0-9)

7G04

T6TF4AFG-0003

TUN-VIPER-RX-DATA

AUDIO/VIDEO

TUNNELBUS

PMX-MA

7L50

K4D261638F

PNX-MDATA

PNX-MCLK-P

PNX-MCLK-N

12

13

15

16

1G50

18

5J54

TXPNXC-

TXPNXCLK-

T

TXPNXD-

TXPNXE-

5J56

5J58

5J60

TXPNXB-

5J50

5J52

TXPNXA-

MP-R(0-9)

MP-ROUT

MP-G(0-9)

MP-GOUT

MP-B(0-9)

MP-BOUT

HSYNC

VSYNC

SOG

R/PR

G/Y

B/PB

PNX2015

VIPER

PACIFIC 3

PICTURE ENHANCEMENT

DDR

SDRAM

16Mx16

10

11

12

22

23

25

33

34

1

2

3

4

6

7

9

BE1

BE1

BE1

BE1

BE1

BE1

BE1

BE1

BE1

BE1

B3a,B7b

B3a,B7b

B3a,B7b

B4a

B3a

B3a

B3b

B5c

B3a,B7b

B3a,B7b

B3a,B7b

B7b

B7b

B3a

B3a

B3a

B3a

B4A,B7a

B3a

B4e

N.C

N.C

N.C

B3f

B3f

B3f

B3f

B3f

B3f

B3f

B3f

B3f

B3f

TUN-VIPER-TX-DATA

TUNNELBUS

B4C

DV I/O INTERFACE

B4B

19

21

22

24

25

27

28

DDR INTERFACE

MP-CLKOUT

MP-OUT-FFIELD

MP-OUT-HS

MP-OUT-VS

MP-OUT-DE

MP-CLK

DV-OUT-FFIELD

MP-HS

MP-VS

MP-DE

116

115

109

114

J29

J28

J30

J27

K26

DV1F-CLK

DV2A-CLK

DV3F-CLK

7V01

K4D551638F

DDR

SDRAM 1

7V02

K4D551638F

DDR

SDRAM 2

MM_DATA

MM_A(0-12)

DDR INTERFACE

EF

7C32

AG28

AJ30

DAC-CVBS

C-MON-OUT

Y-CVBS-MON-OUT

B3f

B3f

Video

output

formatter

VHREF

timing

generator

Termination

resistance

control

Termination

resistance

control

HDMI

receiver

ADC

Slicers

Activity

detection &

sync selec.

Sync

seperator

Clocks

generator

HDCP

Derepeater

Upsample

M135-CLK

Line time

measuremebt

I2C slave

interface

LVDS_AN

LVDS_AP

LVDS_BN

LVDS_BP

LVDS_CN

LVDS_CP

LVDS_CLKN

LVDS_CLKP

LVDS_DN

LVDS_DP

LVDS_EN

LVDS_EP

B26

C26

A25

B25

D25

E25

C23

D23

B24

C24

E24

F24

45

46

MCLK_P

MCLK_N

A17

A16

B4D

DV-HREF

DV-VREF

DV-FREF

AH9

AJ9

AK9

DV1_CLK

DV2_CLK

DV3_CLK

AD28

AF30

AK28

RGB_HSYNC

RGB_VSYNC

RGB_CLK_IN

RGB_UD

RGB_DE

RIN (0-9)

GIN (0-9)

BIN (0-9)

DV1_DATA(0-9)

DV2_DATA(0-9)

DV3_DATA(0-9)

AUDIO/VIDEO

B4A

AV6_VSYNC

G2

AVP2_VSYNC2

AV2_FBL

L2

AVP2_HSYNCFBL2

B3f

B3f

B3C

B3A

IF-TER2

B5C

B5C

B5B

AVIP-1

AVIP-2

COLUMBUS

3D Comb

filter and

noice

reduction

MUX

LVDS_TX

1SD+1HD

YUV

Video in

Memory

based scaler

VO-1

Video MPEG

decoder

VIP

South tunnel

North tunnel

Memory

controller

LVDS

CONNECTOR

TO SCREEN

PMX-MA(0-12)

PNX-MDATA

(0-15)

Memory

controller

5 Layer

primary

video out

HD/VGA/

656

Video

TS

router

Tunnel

Dual

con

acces

Temporal

noise redux

Scaler and

de-interlacer

250Mhz

MIPS32

CPU

DVD

CSS

Dual SD

single HD

MPE2 decoder

2D DE

2-Layer

secondary

video out

VO-2

1

VDISP

2

3

4

DV1F

To

DV1of VIPER

BUFFER

7P76

7P77

DATA

7B30

VSYNC-HIRATE

7B31

VSYNC-HIRATE

B5A

B5A

VSYNC-HIRATE

HSYNC-HIRATE

AD27

AE28

BE

B7A

AK8

EF

EF

EF

7A01

7A02

EF

EF

EF

7A20

7A21

B5C

STANDBY

PROCESSOR

See

Block digram

Control

7LA7

M25P05

512K

FLASH

SPI-SDO

SPI-CLK

SPI-CSB

SPI-WP

5

6

1

3

STANDBY

B4E

DV

1

F

1

7

8

1T41

14

AGC

IF

MIX

OUT

AMP

OUT

OOB

1

ADC

QAM 8VSB

Demodulator

ADC

QPSK

Demodulator

Micro-

Controller

GPIO

FEC

ADC

MPEG_DATA

DRX-POD-(9)

CRX-POD-A(8)

MUX

7P13

63 64

11

12

I2C TUNER

119

120

DTV CABLE AND

TERRESTRIAL

RECEIVER

AGC

IN

AMP

IN

OOB

SAW 44MHz

IF-OUT

IF-1

IF-2

VIDEO

S VIDEO

VIDEO

V

PB/B

VIDEO

H

Y/G

PR/R

S VIDEO

EXT2

R16

M16

T12

R12

T14

R14

T9

R9

T7

R9

EXT1

PB/B

Y/G

PR/R

BE1

BE1

BE1

EXT3

G26

AH16

AH19

AG25

AK10

AH10

AG10

AJ27

POD

From

POD

B10C