31

UF-580/590/780/790

DX-600/800

DEC 2003

Ver 2.00

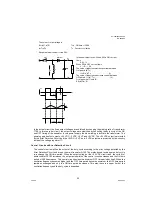

1.1.15 LAN Control Circuit (DX-600/800 only)

LAN Controller

1. LAN Controller (IC1)

This conforms to IEEE 802.3 Ethernet Controller. The CPU (SC PCB) bus is directly connected and the

data interrupt is controlled by pLANINT. The 25 MHz clock is supplied by OSC 1. The LAN Controller

for the system timing clock divides the frequency provided from OSC1. The clock signal is also

supplied for the Manchester encoding/decoding circuit for data conversion.

The LAN Controller is a mixed signal Analog/Digital device that implements the MAC and PHY portion

of the CSMA/CD protocol at 10 and 100Mbps.

The LAN controller contains a built in 8 KByte RAM for transmission and reception buffer.

2. EEPROM (IC2)

This memory stores the configuration registers and MAC (Media Access Control) address for the LAN

controller. Data is transferred to LAN controller (serial transfer) when the power is turned "On". The

MAC address for the LAN controller represents the location on the LAN.

3. Filter Transformer (T1)

A choke module transformer with a EMI filter. The output TX signal from the LAN controller is

differentiated and transmitted on to the LAN via this module. Similarly, the input RX signal

(differential input pair) is terminated by an externally connected 75 ohms resistor and input to the LAN

controller via this module.

4. Ethernet Interface

Provides the 10Base-T/100Base-TX Ethernet interface.

FROM 4MB

Image Memory

(IC10)

LANB

PCB

LANC

PCB

CPU

V850E/MA1

(IC1)

SHINE

DZAC000273

(IC3)

FROM 4MB

Program

(IC9)

MN86075

(IC30)

MODEM

MN195006

(I22)

D-BUS

Laser Printer

CCD PCB

Line

Line

Memory

Page

Memory

ECM

Buffer

S-DRAM 8MB

(IC7)

(2)

Transformer

(T1)

LAN Controller

(IC1)

RJ45

LINK

ACTIVITY

INTERNET

(10Base-T/100Base-TX)

(1)

AFE

STLC7550

(IC27)

Summary of Contents for Panafax UF-580

Page 170: ...DZZSM00214...