190

Data Link I/O Response Time

Section 9-3

Network configuration:

8 nodes

Nodes that send messages:

2 nodes

Bytes in all messages sent:

2,012

×

2 bytes

In this example, A to D in the equation have the following values.

A: 4; B: 2; C: 8; D: 7

×

8

The maximum communications cycle delay in token-ring mode would be as

follows:

(4

×

4 + 2

×

2 + 1)

×

(3

×

8 + 7

×

8) = 1,680 (

µ

s)

≅

1.7 (ms)

The rate of change in the communications cycle time when data links are

active would be as follows (refer to 9-2-1 Active Data Links):

(111 + 1.7)/111

×

100

≅

101.5 (%)

The rate of change in the communications cycle time when data links are

inactive would be as follows (refer to 9-2-2 Inactive Data Links):

(32 + 1.7)/32

×

100

≅

105.3 (%)

9-3

Data Link I/O Response Time

When accurate communications timing is required, you need to understand

data exchange timing and the time required for data transmission and recep-

tion via data links. Use the information described in this section as reference

information for system construction.

9-3-1

Data Exchange Timing

This section describes data exchange timing for data links between the Con-

troller Link Unit and the PLC’s CPU Unit. Data exchange is executed as inter-

rupt processing during CPU Bus Unit or Programming Device/Host Link

servicing performed by the CPU Unit. This interrupt processing is executed

each time data exchange between the local node and each node connected

via a data link is completed.

Data exchange timing differs depending on the CPU Unit model and the CPU

Unit the Execute Process (asynchronous or synchronous) specified in PLC

Setup, as described below.

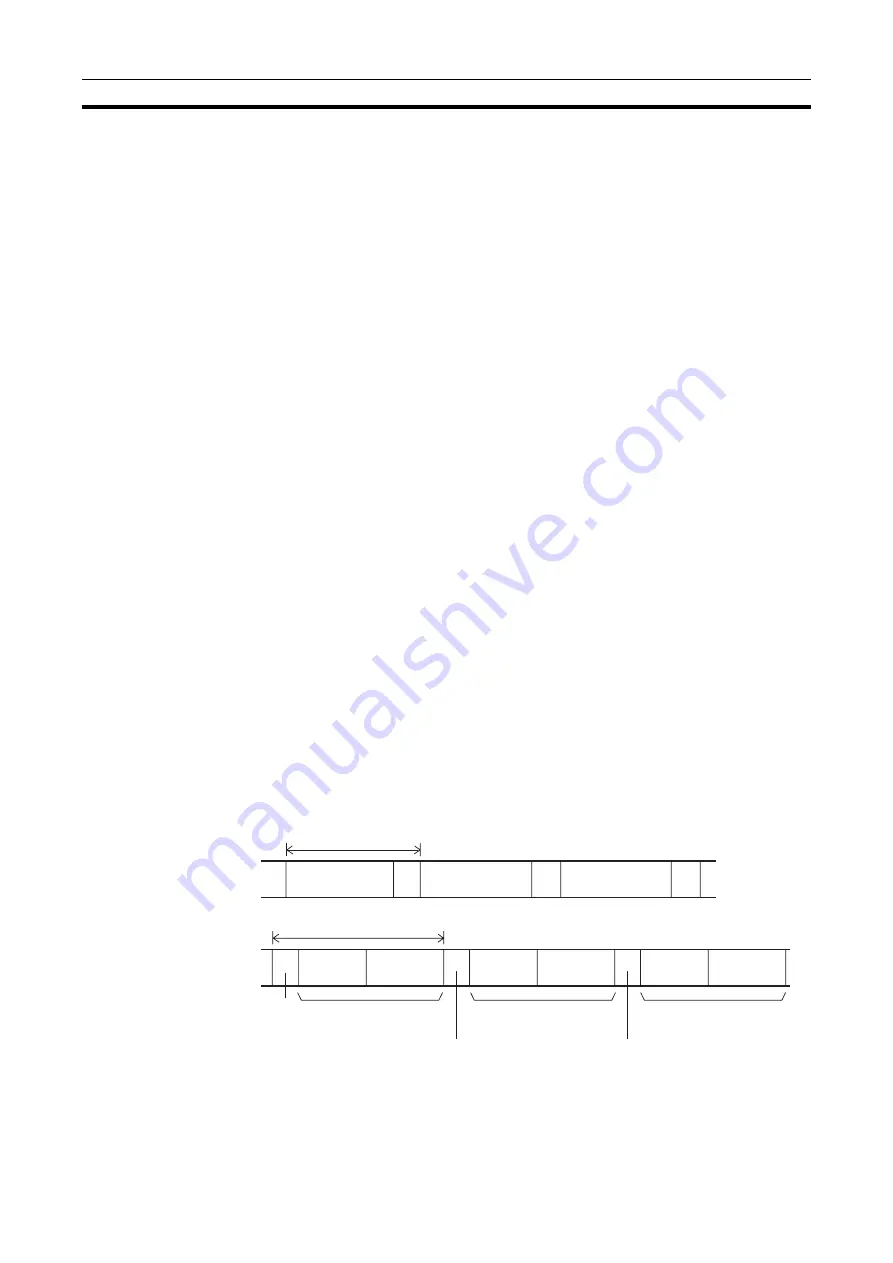

CVM1 and CV-series PLCs

Under Asynchronous

Operation

When a CVM1 or CV-series CPU Unit is operating in asynchronous mode,

data exchange with the Controller Link Unit is executed as interrupt process-

ing during peripheral processing, regardless of the cycle time of PLC instruc-

tion execution. Data exchange timing is as follows:

More than one data exchange can be executed during a PLC cycle, depend-

ing on the data exchange timing. If interrupt processing for data exchange is

executed, the peripheral servicing interval will be lengthened by the time

required for the interrupt processing (see 9-3-2 Data Processing Time on

page 191).

Instruction execution

PLC cycle time

Execution

I/O refreshing

PLC processing

Peripheral processing

Peripheral servicing interval

Basic processing

CPU Bus

Unit service

Programming

Device/Host Link

service

Interrupt processing

for data exchange

Execution

Execution

I/O refreshing

I/O refreshing

Interrupt processing

for data exchange

Interrupt processing

for data exchange

Basic processing

CPU Bus

Unit service

Programming

Device/Host Link

service

CPU Bus

Unit service

Programming

Device/Host Link

service

Basic processing

Summary of Contents for CS1W-CLK12-V1

Page 3: ...iv ...

Page 5: ...vi ...

Page 9: ...x TABLE OF CONTENTS ...

Page 11: ...xii ...

Page 59: ...42 Component Names and Functions Section 3 1 Dimensions Unit mm ...

Page 62: ...45 Component Names and Functions Section 3 1 Dimensions Unit mm ...

Page 91: ...74 CVM1 and CV series Optical Ring Controller Link Units Section 4 2 ...

Page 108: ...91 Setting Data Links Section 5 2 Device Information Setting Data Link Tables ...

Page 125: ...108 Checking Data Link Status Section 5 4 ...

Page 181: ...164 Setting Routing Tables Section 7 4 ...

Page 199: ...182 Memory Areas Related to Duplex Operation Section 8 6 ...

Page 275: ...258 Handling Precautions Section 10 7 ...

Page 298: ...281 CS series Optical Bus Controller Link Units Appendix C Dimensions Unit mm 101 35 130 ...

Page 299: ...282 CS series Optical Bus Controller Link Units Appendix C ...