ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

340

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

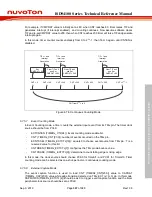

6.7.3

Block Diagram

Timer Controller block diagram is shown below.

Timer

Interrupt

0

1

0

1

Reset counter

+

-

=

Reset counter

Load

CNTPHASE

(TIMERx_EXTCTL[0])

CAPEN

(TIMERx_EXTCTL[3])

TMRx_CLK

TM0 ~ TM3

EXTCNTEN

(TIMERx_CTL[24])

RSTCNT(TIMERx_CTL[26]

CNTEN(TIMERx_CTL[30]

8 - bit

Prescale

24 - bit up counter

24 - bit CMPDAT

(TIMERx_CMP[23:0])

WKEN

(TIMERx_CTL[23])

TWKF

(TIMERx_INTSTS[1])

TIF

(TIMERx_INTSTS[0])

CAPIEN

(TIMERx_EXTCTL[5])

INTEN

(TIMERx_CTL[29])

24– bit CAPDAT

(TIMERx_CAP[23:0])

24– bit CNT

(TIMERx_CNT[23:0])

CAPIF

(TIMERx_

EINTSTS[0])

CAPFUNCS

(TIMERx_EXTCTL[4])

Timer

Wakeup

TM0_EXT ~ TM3_EXT

00

01

10

CAPEDGE

(TIMERx_EXTCTL[2:1])

1

0

Figure 6.7-1 Timer Controller Block Diagram

Timer clock source can be from:

-

HXT

-

LXT

-

PCLK1

-

External clock on TMx pin, x=0, 1, 2 or 3.

-

LIRC

-

HIRC

Note: in PWM mode clock source selection is different, as explanation follows.

.