left-justified and padded with 4 zeros in the LSBs. You must rout DStarA to the CLIP

from LabVIEW FPGA. The data is clocked out of the CLIP on Data Clock.

Related Information

Clocking

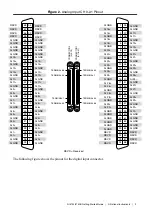

The NI 5752/5752B clock source controls the sample rate and other timing functions on the

device. The following table contains information about the possible NI 5752/5752B clock

sources.

Table 3.

Sample Clock Sources

Clock

Notes

Frequency

Range

50 MHz

onboard clock

—

25 MHz to

50 MHz

Sync Clock

(DStarA)

Sync Clock (DStarA) is only available on NI PXI

Express FlexRIO FPGA modules (such as the

NI PXIe-796xR). DStarA is not available on

NI-793xR controllers for FlexRIO or NI PXI FlexRIO

FPGA modules (such as the NI PXI-795xR). On PXI

Express modules, Sync Clock is driven by the DStarA

from the PXI/PXIe backplane.

If you change the frequency of Sync Clock (DStarA)

or CLK IN (when used as the Sample Clock), you

must assert Force Initialization.

CLK IN (front

panel SMB)

If you change the frequency of Sync Clock (DStarA)

or CLK IN (when used as the Sample Clock), you

must assert Force Initialization.

Related Information

For more information about clock sources, refer to the FlexRIO Help.

Worldwide Support and Services

The NI website is your complete resource for technical support. At

access to everything from troubleshooting and application development self-help resources to

email and phone assistance from NI Application Engineers.

NI 5752/5752B Getting Started Guide

|

© National Instruments

|

13