345

Chapter 10

16-bit Inverter Timer/Counter R

User’s Manual U16580EE3V1UD00

10.4.2 Compare register rewrite operation

In the PWM mode, high-accuracy T-PWM mode, PWM mode with dead time, external trigger pulse

output mode, and triangular wave PWM mode, the reload function is valid. (In all other modes,

reload-related settings are invalid.)

The compare/control registers with the reload function are listed below.

•

TRnCCR0 to TRnCCR5

•

TRnOPT1

Compare registers with the reload function can be rewritten in the following modes.

• Anytime rewrite mode

In this mode, each compare register is updated independently, and when a compare register is

written to, the register is updated to the value written during anytime write access.

• Reload mode (batch rewrite)

When the TRnCCR1 register is written to, all the registers are updated at the next reload timing

(reload).

Reload does not occur even if a register other than the TRnCCR1 register is written to.

A reload request flag (TRnRSF) is provided.

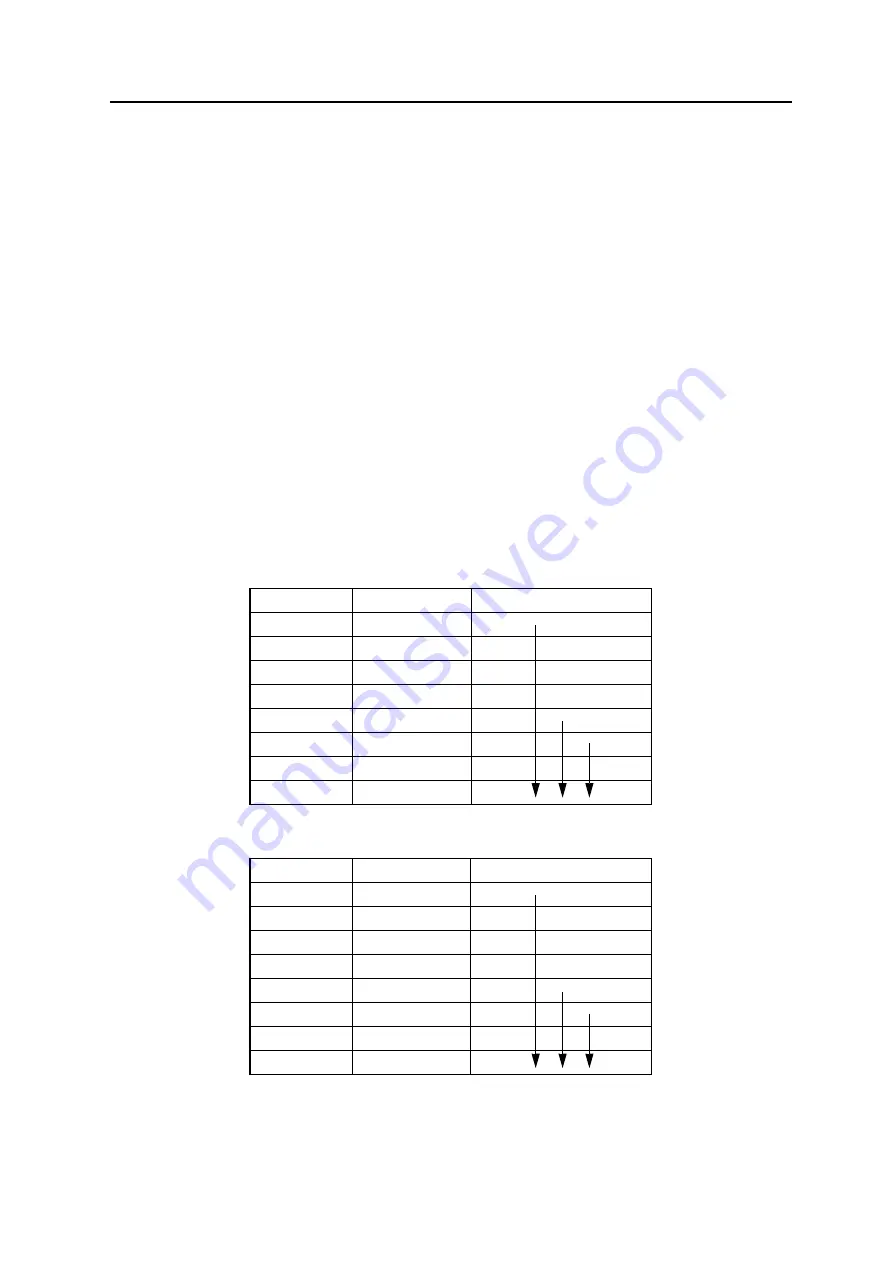

The compare register can be rewritten using DMA transfer. DMA transfer is performed as follows.

Note:

Dummy data transfer

Address

Register Name

DMA Transfer Sequence

FFFFF590H

TR0CCR5

FFFFF592H

TR0CCR4

FFFFF594H

-

Note

FFFFF596H

-

Note

FFFFF598H

TR0CCR0

FFFFF59AH

TR0CCR3

FFFFF59CH

TR0CCR2

FFFFF59EH

TR0CCR1

Address

Register Name

DMA Transfer Sequence

FFFFF5D0H

TR1CCR5

FFFFF5D2H

TR1CCR4

FFFFF5D4H

-

Note

FFFFF5D6H

-

Note

FFFFF5D8H

TR1CCR0

FFFFF5DAH

TR1CCR3

FFFFF5DCH

TR1CCR2

FFFFF5DEH

TR1CCR1

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......