Programming Model

http://www.motorola.com/computer/literature

3-67

3

ram e/f/g/h en ram e/f/g/h en enables accesses to the corresponding block of

SDRAM when set, and disables them when cleared.

Note that ram a/b/c/d en are located at $FEF80010 (refer to the

section on SDRAM Enable and Size Register (Blocks A,B,C,D)

in a previous section). They operate the same for blocks A-D as

these bits do for blocks E-H.

ram e/f/g/h siz0-3 These control bits define the size of their corresponding block of

SDRAM. Note that ram a/b/c/d siz0-3 are located at

$FEF80010. They operate identically for blocks A-D as these

bits do for blocks E-H. The table associated with the previous

section on blocks A,B,C,D shows how these bits relate to the

block configuration.

SDRAM Base Address Register (Blocks E/F/G/H)

Writes to this register must be enveloped by a period of time in which no

accesses to SDRAM occur. The requirements of the envelope are that all

SDRAM accesses must have completed before the write starts and none

should begin until after the write is done. A simple way to do this is to

perform at least two read accesses to this or another register before and

after the write.

Additionally, sometime during the envelope, before or after the write, all

of the SDRAMs’ open pages must be closed and the Hawk’s open page

tracker reset. The way to do this is to allow enough time for at least one

SDRAM refresh to occur by waiting for the 32-Bit Counter to increment

at least 100 times. The wait period needs to happen during the envelope.

RAM E/F/G/H BASE These control bits define the base address for their block’s

SDRAM. RAM E/F/G/H BASE bits 0-7/8-15/16-23/24-31

correspond to PowerPC60x address bits 0 - 7. For larger SDRAM

sizes, the lower significant bits of RAM E/F/G/HBASE are

ignored. This means that the block’s base address will always

appear at an even multiple of its size. Remember that bit 0 is

MSB.

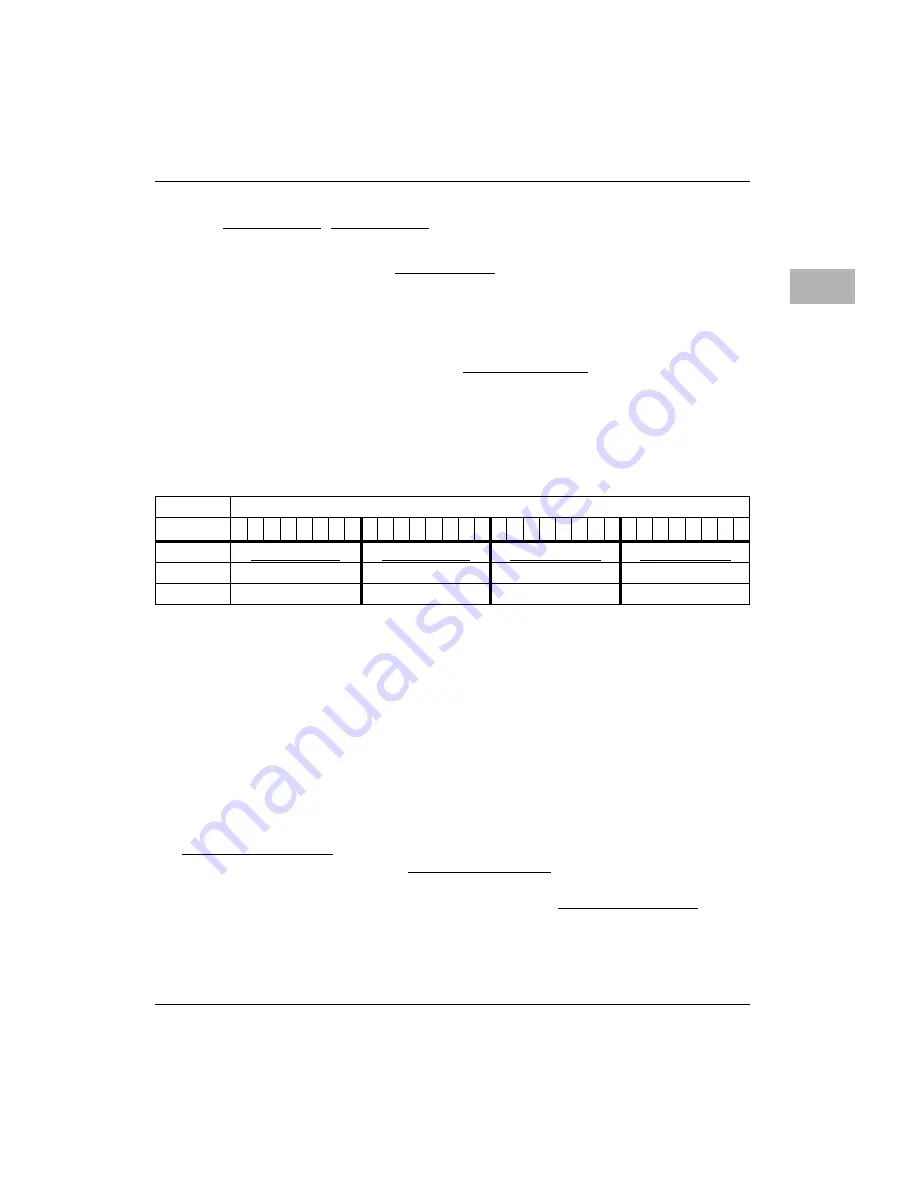

Address

$FEF800C8

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

RAM E BASE

RAM F BASE

RAM G BASE

RAM H BASE

Operation

READ/WRITE

READ/WRITE

READ/WRITE

READ/WRITE

Reset

0 PL

0 PL

0 PL

0 PL

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...