3-30

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

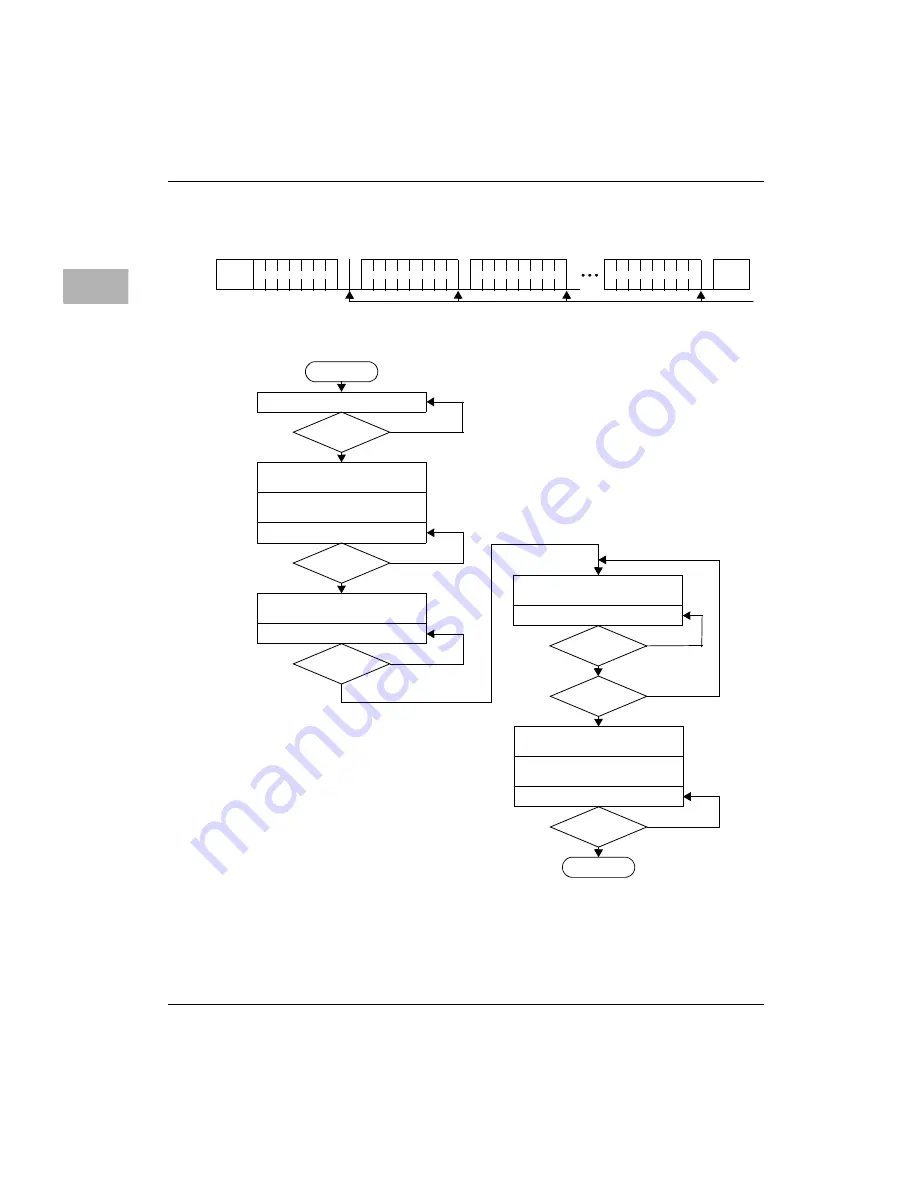

Figure 3-8. Programming Sequence for I

2

C Page Write

READ I

2

C STATUS REG

CMPLT=1?

N

Y

LOAD “WORD ADDR 1” TO

I

2

C TRANSMITTER DATA REG

LOAD “DATA1 ... DATA n” TO

I

2

C TRANSMITTER DATA REG

READ I

2

C STATUS REG

CMPLT=ACKIN=1?

N

Y

READ I

2

C STATUS REG

CMPLT=ACKIN=1?

N

Y

LOAD “$09” (START CONDITION) TO

I

2

C CONTROL REG

LOAD “DEVICE ADDR+WR BIT” TO

I

2

C TRANSMITTER DATA REG

READ I

2

C STATUS REG

CMPLT=ACKIN=1?

N

Y

LOAD “$05” (STOP CONDITION) TO

I

2

C CONTROL REG

LOAD “DUMMY DATA” TO

I

2

C TRANSMITTER DATA REG

READ I

2

C STATUS REG

CMPLT=1?

N

Y

START

STOP

SDA

S

B

M

DEVICE ADDR

W

R

A

C

K

WORD ADDR 1

A

C

K

DATA 1

A

C

K

ACK from Slave Device

END

BEGIN

*

*

*

(*)

:

Stop condition should be generated to abort the transfer after a software wait loop (~1ms) has been expired

DATA n

A

C

K

LAST BYTE ?

N

Y

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...