Memory Maps

MVME197LE/D2

3-23

3

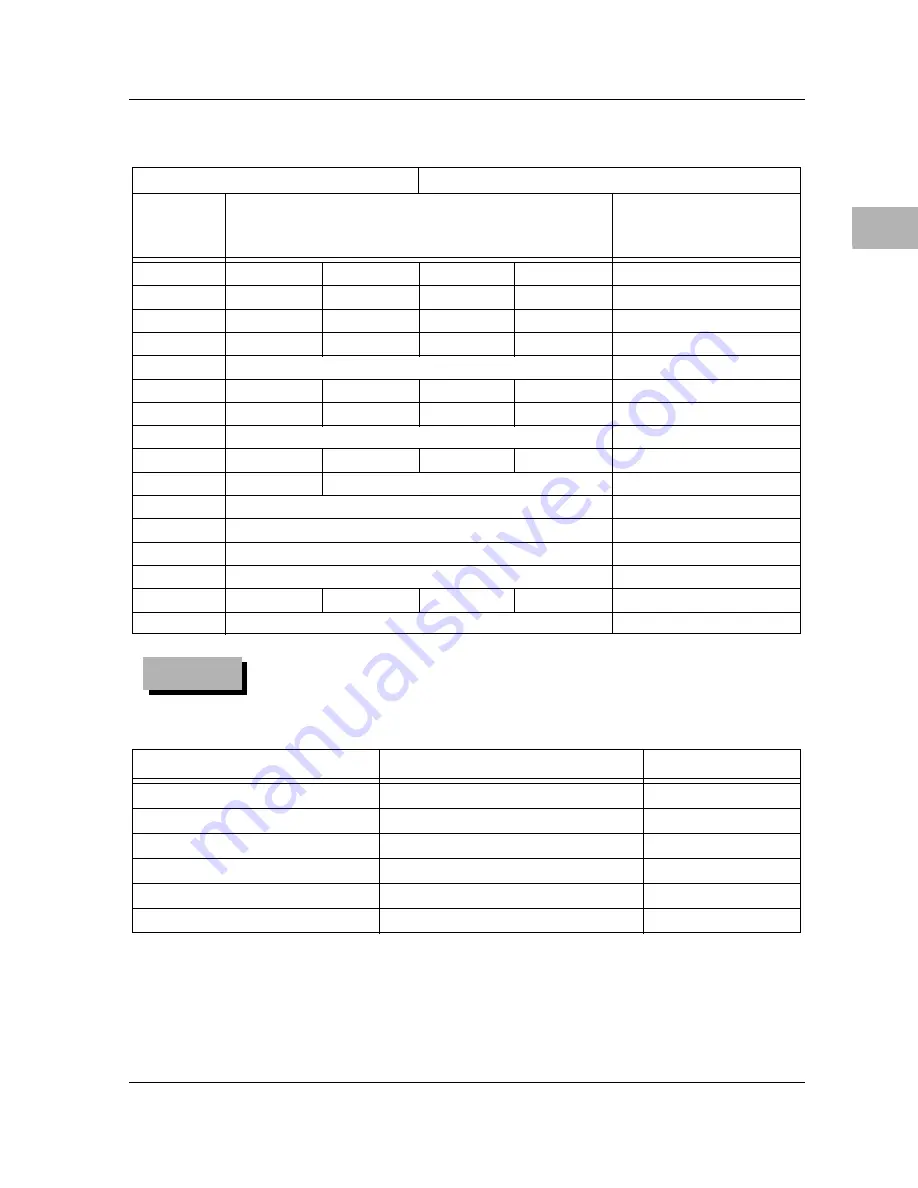

Table 3-11. 53C710 SCSI Memory Map

N

ote

Accesses may be 8-bit or 32-bit, but not 16-bit.

Table 3-12. MK48T08 BBRAM, TOD Clock Memory Map

53C710 Register Address Map

Base Address is $FFF47000

Big

SCRIPTs Mode

Endian

and Little

Mode

Endian Mode

00

SIEN

SDID

SCNTL1

SCNTL0

00

04

SOCL

SODL

SXFER

SCID

04

08

SBCL

SBDL

SIDL

SFBR

08

0C

SSTAT2

SSTAT1

SSTAT0

DSTAT

0C

10

DSA

10

14

CTEST3

CTEST2

CTEST1

CTEST0

14

18

CTEST7

CTEST6

CTEST5

CTEST4

18

1C

TEMP

1C

20

LCRC

CTEST8

ISTAT

DFIFO

20

24

DCMD

DBC

24

28

DNAD

28

2C

DSP

2C

30

DSPS

30

34

SCRATCH

34

38

DCNTL

DWT

DIEN

DMODE

38

3C

ADDER

3C

Address Range

Description

Size (Bytes)

$FFFC0000

-

$FFFC0FFF

User Area

4096

$FFFC1000

-

$FFFC10FF

Networking Area

256

$FFFC1100

-

$FFFC16F7

Operating System Area

1528

$FFFC16F8

-

$FFFC1EF7

Debugger Area

2048

$FFFC1EF8 -

$FFFC1FF7

Configuration Area

256

$FFFC1FF8

-

$FFFC1FFF

TOD Clock

8

Summary of Contents for MVME197LE

Page 1: ...MVME197LE Single Board Computer User s Manual MVME197LE D2 ...

Page 12: ...xii ...

Page 14: ...xiv ...

Page 22: ...Hardware Preparation and Installation 2 2 User s Manual 2 ...

Page 30: ...Hardware Preparation and Installation 2 10 User s Manual 2 ...

Page 37: ...Memory Maps MVME197LE D2 3 7 3 ...

Page 40: ...Operating Instructions 3 10 User s Manual 3 ...

Page 42: ...Operating Instructions 3 12 User s Manual 3 ...

Page 44: ...Operating Instructions 3 14 User s Manual 3 ...

Page 46: ...Operating Instructions 3 16 User s Manual 3 ...

Page 48: ...Operating Instructions 3 18 User s Manual 3 ...

Page 60: ...Functional Description 4 2 User s Manual 4 ...