12-4

MPC8240 Integrated Processor User’s Manual

Internal Buffers

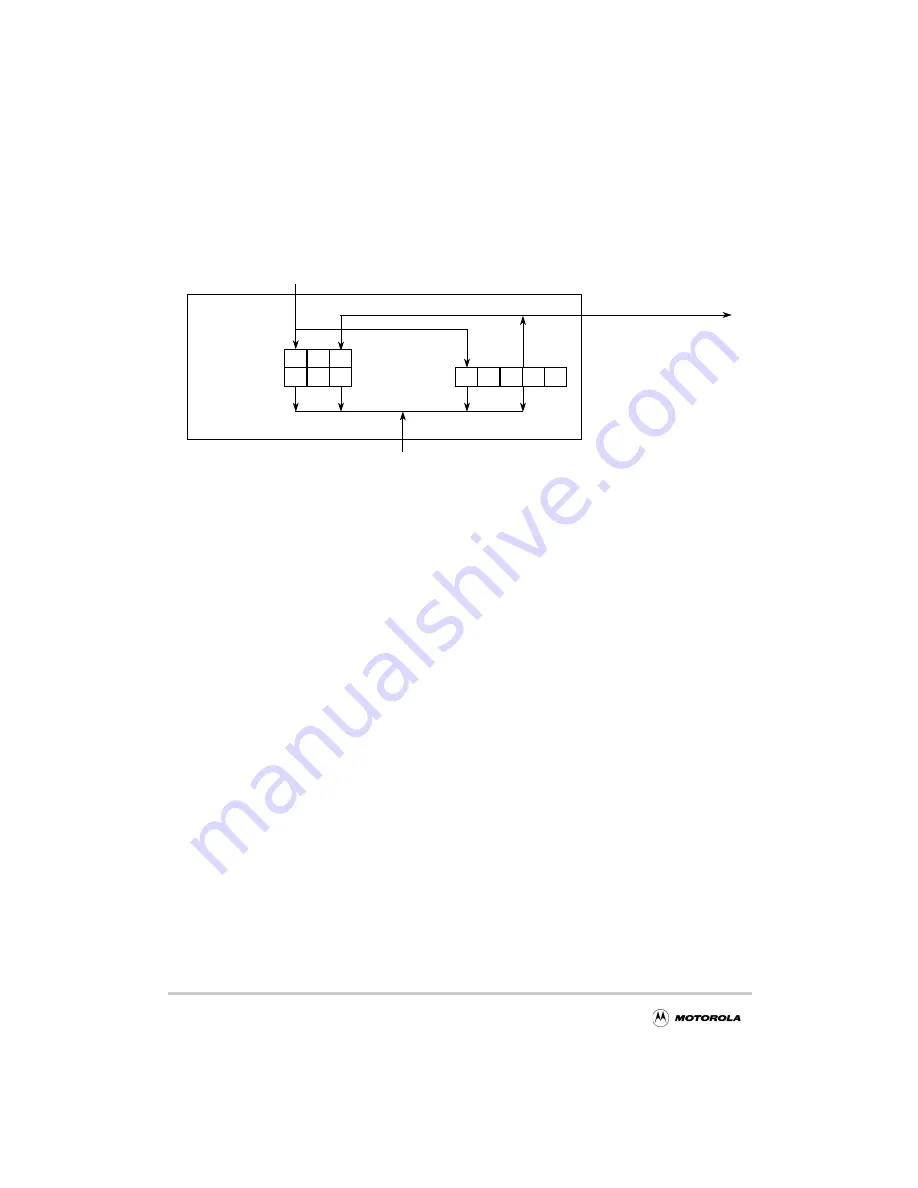

Figure 12-3 shows the address and data buffers between the peripheral logic bus and the

PCI bus.

Figure 12-3. Processor/PCI Buffers

12.1.2.1 Processor-to-PCI-Read Buffer (PRPRB)

Processor reads from PCI require buffering for two primary reasons. First, the processor

bus uses a critical-word-first protocol, while the PCI bus uses a zero-word-first protocol.

The MPC8240 requests the data zero-word-first, latches the requested data, and then

delivers the data to the processor core critical-word-first.

The second reason is that if the target for a processor read from PCI disconnects part way

through the data transfer, the MPC8240 may have to handle a local memory access from an

alternate PCI master before the disconnected transfer can continue.

When the processor requests data from PCI space, the data received from PCI is stored in

the PRPRB until all requested data has been latched. The CCU does not terminate the

address tenure of the internal transaction until all requested data is latched in the PRPRB.

If the PCI target disconnects in the middle of the data transfer and an alternate PCI master

acquires the bus and initiates a local memory access, the CCU retries the ongoing internal

transaction with the processor core so that the incoming PCI transaction can be snooped. A

PCI-initiated access to local memory may require a snoop transaction on the internal

peripheral logic bus and also a copyback. The CCU does not provide the data to the

peripheral logic bus (for the processor to PCI read transaction) until all outstanding snoops

for PCI writes to local memory have completed.

Note that if a processor read from a PCI transaction is waiting for a PCMWB snoop to

complete (that is, data has been latched into PRPRB from the PCI bus but has not yet

returned to the processor—perhaps the processor must retry the read), all subsequent

requests for PCI writes to local memory will be retried on the PCI bus.

PCI Address/Data

Processor/Memory Data

Processor Address/Control

Processor/PCI

Write Buffers

Read Buffer

A0 D0 D1

A1 D2 D3

A

D0 D1 D2 D3

Processor/PCI

(PRPWBs)

(PRPRB)

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...