10-10

MPC8240 Integrated Processor User’s Manual

I

2

C Register Descriptions

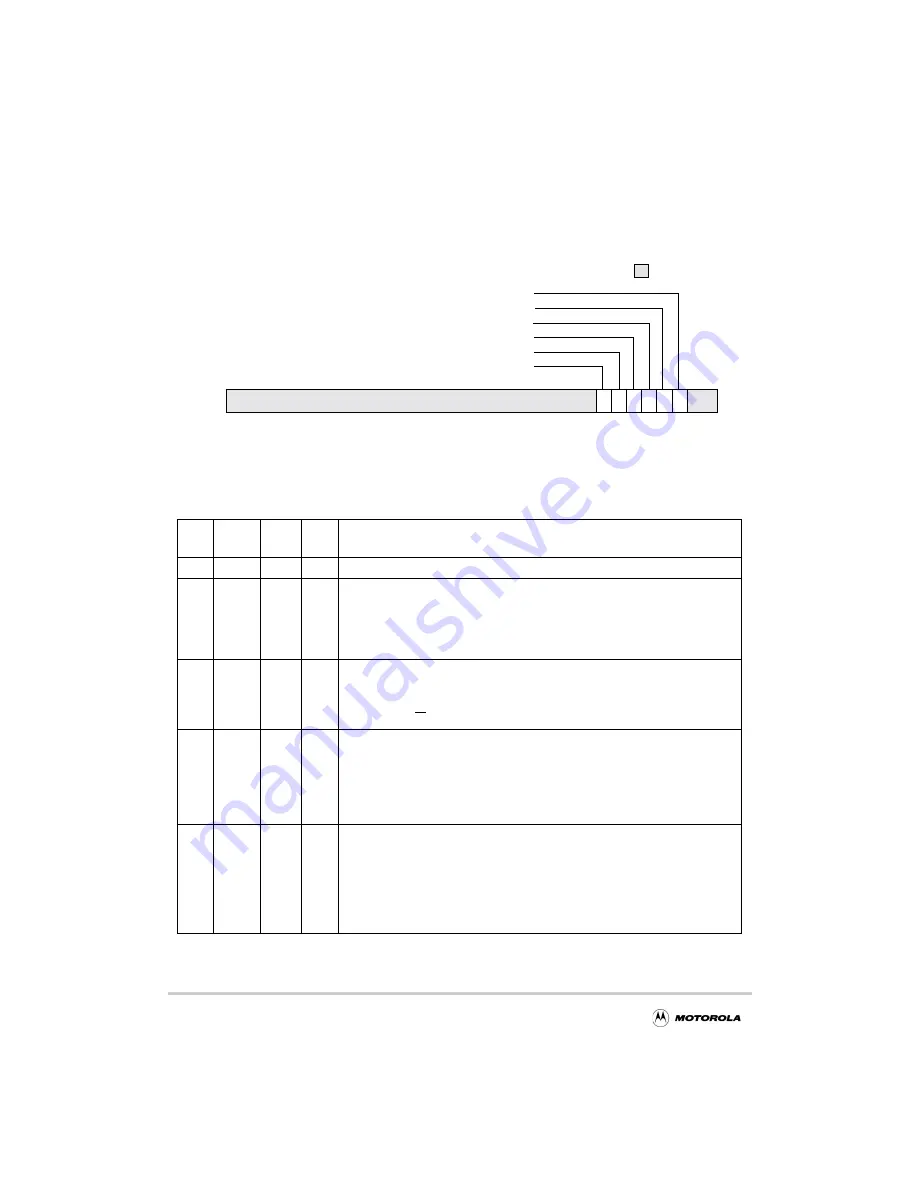

10.3.3 I

2

C Control Register (I2CCR)

The I2CCR controls the modes of the I

2

C interface, and is shown in Figure 10-5.

Figure 10-5. I

2

C Control Register (I2CCR)

Table 10-3 describes the bit settings of the I2CCR.

Table 10-6. I2CCR Field Descriptions—Offset 0x0_3008

Bits

Name

Reset

Value

R/W

Description

31–8

—

R

Reserved

7

MEN

0

R/W

Module enable. This bit controls the software reset of the I

2

C module.

0 The module is reset and disabled. When low, the interface is held in reset. In this

state, all the registers except I2CDR can still be accessed.

1 The I

2

C module is enabled. This bit must be set before any other control register

bits have any effect. All I

2

C registers for slave receive or master START can be

initialized before setting this bit. Refer to Section 10.2.6, “Arbitration Procedure.”

6

MIEN

0

R/W

Module interrupt enable

0 Interrupts from the I

2

C module are disabled. This does not clear any pending

interrupt conditions.

1 Interrupts from the I

2

C module are enabled. When an interrupt condition occurs,

an interrupt (int) is generated, provided I2CSR[MIF] is also set.

5

MSTA

0

R/W

Master/slave mode START

0 Slave mode. When this bit is changed from a 1 to 0, a STOP condition is

generated and the mode changes from master to slave.

1 Master mode. When this bit is changed from a 0 to 1, a START condition is

generated on the bus, and the master mode is selected.

The MSTA bit is cleared without generating a STOP condition when the master

loses arbitration. See Section 10.2.6, “Arbitration Procedure.”

4

MTX

0

R/W

Transmit/receive mode select. This bit selects the direction of the master and slave

transfers. When configured as a slave, this bit should be set by software according

to I2CSR[SRW]. In master mode, the bit should be set according to the type of

transfer required. Therefore, for address cycles, this bit will always be high.

0 Receive mode

1 Transmit mode

The MTX bit is cleared when the master loses arbitration.

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0

31

8

7

6

5

4

3

2

1

0

Reserved

MEN

MIEN

MSTA

MTX

TXAK

RSTA

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...