6-74

MPC8240 Integrated Processor User’s Manual

ROM/Flash Interface Operation

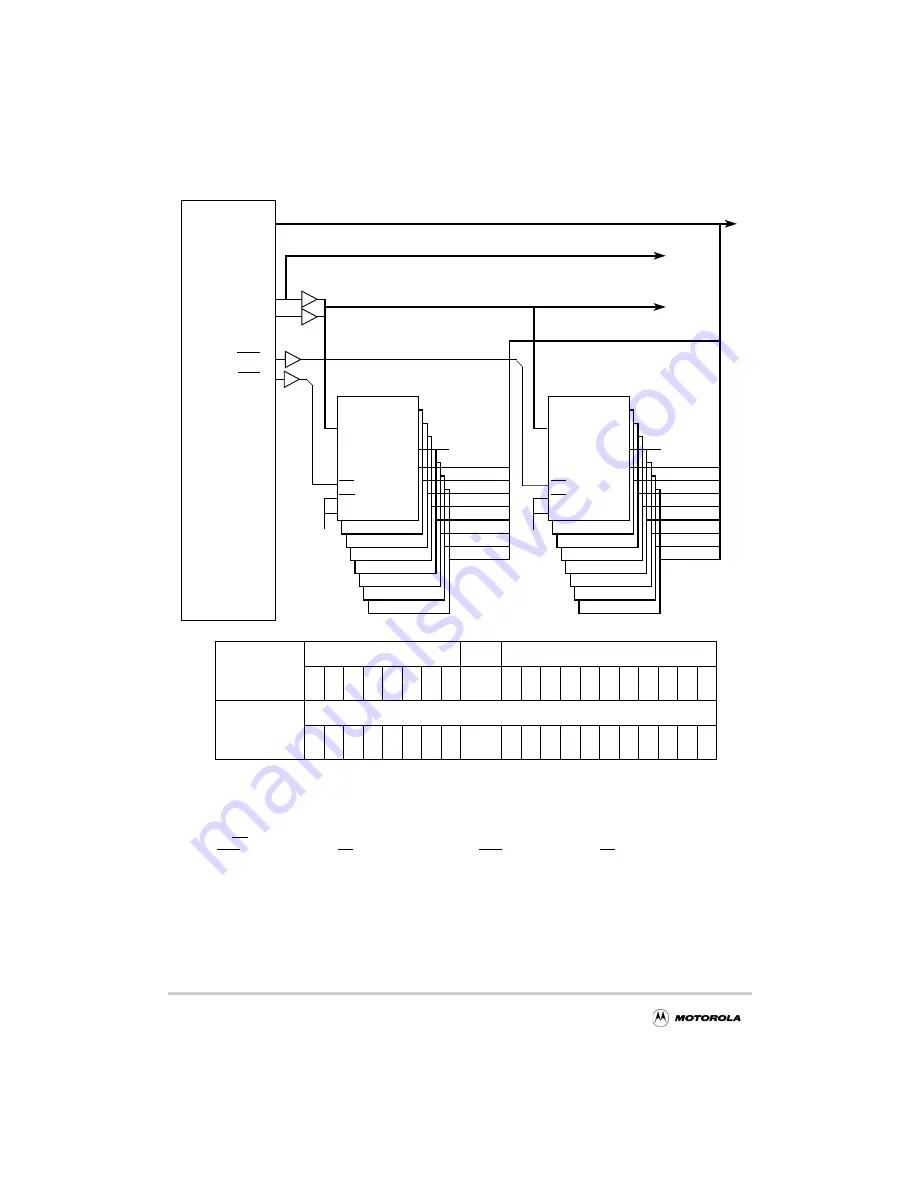

Figure 6-50. 16-Mbyte ROM System Including Parity Paths to DRAM—64-Bit Mode

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A(11-0)

2Mx8 SDRAM

DQ(7-0)

BA(1-0)

CAS

CS

RAS

WE

CKE

CLK

A(11-0)

2Mx8 SDRAM

DQ(7-0)

BA(1-0)

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CE

BHE

A[0:18]

1Mx8 ROM

Q[7:0]

A[-1]

MDH[0:7]

MDH[8:15]

MDH[16:23]

MDH[24:31]

MDL[0:7]

MDL[8:15]

MDL[16:23]

MDL[24:31]

MDH[0:7]

RCS[0]

PAR[0:7]

SDMA[12:0]

MDH[0:31]

MDL[0:31]

MPC8240

Data Path to/from DRAM/SDRAM Array

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

CAS

CS

RAS

WE

CKE

CLK

A(11-0)

2Mx8 SDRAM

DQ(7-0)

BA(1-0)

CAS

CS

RAS

WE

CKE

CLK

A(11-0)

2Mx8 SDRAM

DQ(7-0)

BA(1-0)

CAS

CS

RAS

WE

CKE

CLK

A[0-11]

2Mx8 SDRAM

DQ[0-7]

BA[0-1]

MDH[8:15]

MDH[16:23]

MDH[24:31]

MDL[0:7]

MDL[8:15]

MDL[16:23]

MDL[24:31]

RCS[1]

OE

BHE

BHE

BHE

BHE

BHE

BHE

BHE

Q[15:8]

NC

CE

BHE

A[0:18]

1Mx8 ROM

Q[7:0]

A[-1]

OE

Q[15:8]

BHE

BHE

BHE

BHE

BHE

BHE

BHE

NC

GND

GND

Buffers

Parity Path to/from DRAM/SDRAM Array

Address Path to DRAM/SDRAM Array

Notes:

The array of ROM memory devices are 8-Mbit (1M x 8 or 512K x 16) configured for 1M x 8 operation.

A[-1] is the lsb of the ROM memory devices.

BHE connected to GND enables A[-1] as an input and sets Q[15:8] to Hi-Z.

Q[7:0] of the ROM Memory devices are data outputs connected to MDH[0-31] and MDL[0:31].

MDH[0:7] is the most significant byte lane and MDL[24:31] is the least significant byte lane.

All OE and BHE signals are connected to GND.

RCS0 is connected to all CE in Bank 0 (8 Mbytes) and RCS1 is connected to all CE in Bank 1 (8 Mbytes).

1.

2.

3.

4.

5.

6.

Address

Signals

(Outputs)

PAR

SDBA

SDMA

0

1

2

3

4

5

6

7

0

1

0

9

8

7

6

5

4

3

2

1

0

Logical Names

msb

AR

lsb

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

11

1

0

9

8

7

6

5

4

3

2

1

0

SDBA[0]

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...