E-14

MPC8240 Integrated Processor User’s Manual

PowerPC Register Set

14

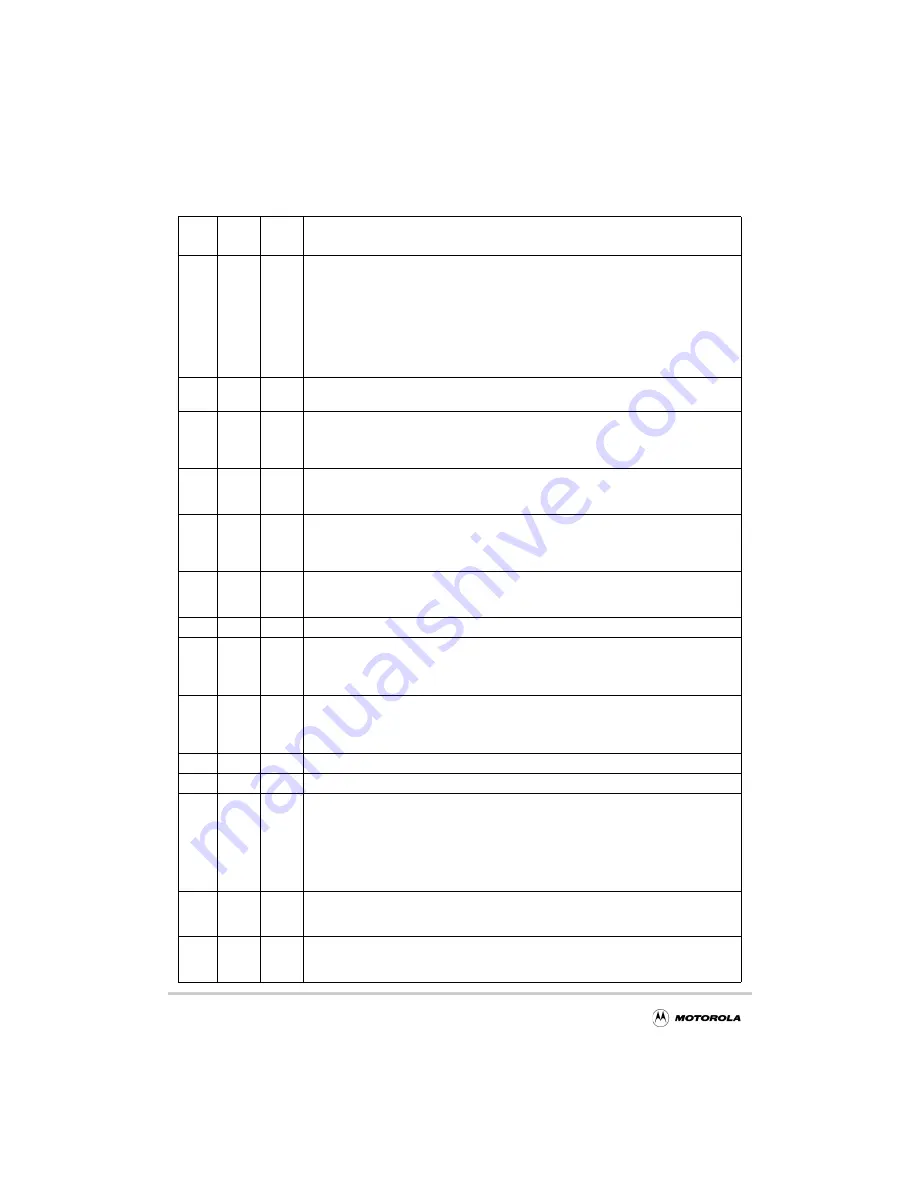

TGPR

0

Temporary GPR remapping (603e-specific)

0 Normal operation

1 TGPR mode. GPR0–GPR3 are remapped to TGPR0–TGPR3 for use by TLB miss

routines.

The contents of GPR0–GPR3 remain unchanged while MSR[TGPR] = 1. Attempts to use

GPR4–GPR31 with MSR[TGPR] = 1 yield undefined results. When this bit is set, all

instruction accesses to GPR0–GPR3 are mapped to TGPR0–TGPR3, respectively. The

TGPR bit is set when an instruction TLB miss, data TLB miss on load or data TLB miss on

store exception is taken. The TGPR bit is cleared by an rfi instruction.

15

ILE

0

Exception little-endian mode. When an exception occurs, this bit is copied into MSR[LE] to

select the endian mode for the context established by the exception.

16

EE

0

External interrupt enable

0 While the bit is cleared, the processor delays recognition of external interrupts and

decrementer exception conditions.

1 The processor is enabled to take an external interrupt or the decrementer exception.

17

PR

0

Privilege level

0 The processor can execute both user- and supervisor-level instructions.

1 The processor can only execute user-level instructions.

18

FP

0

Floating-point available

0 The processor prevents dispatch of floating-point instructions, including floating-point

loads, stores, and moves.

1 The processor can execute floating-point instructions.

19

ME

0

Machine check enable

0 Machine check exceptions are disabled.

1 Machine check exceptions are enabled.

20

FE0

0

Floating-point exception mode 0 (see Table E-9).

21

SE

0

Single-step trace enable

0 The processor executes instructions normally.

1 The processor generates a single-step trace exception upon the successful execution of

the next instruction.

22

BE

0

Branch trace enable

0 The processor executes branch instructions normally.

1 The processor generates a branch trace exception after completing the execution of a

branch instruction, regardless of whether the branch was taken.

23

FE1

0

Floating-point exception mode 1 (see Table E-9).

24

—

0

Reserved

25

IP

1

Exception prefix. The setting of this bit specifies whether an exception vector offset is

prepended with Fs or 0s. In the following description, nnnnn is the offset of the exception

vector.

0 Exceptions are vectored to the physical address 0x000n_nnnn.

1 Exceptions are vectored to the physical address 0xFFFn_nnnn.

In most systems, IP is set to 1 during system initialization, and then cleared to 0 when

initialization is complete.

26

IR

0

Instruction address translation

0 Instruction address translation is disabled.

1 Instruction address translation is enabled.

27

DR

0

Data address translation

0 Data address translation is disabled.

1 Data address translation is enabled.

Table E-8. MSR Bit Settings (Continued)

Bit(s)

Name

Reset

Value

Description

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...