16-4

Watchpoint Registers

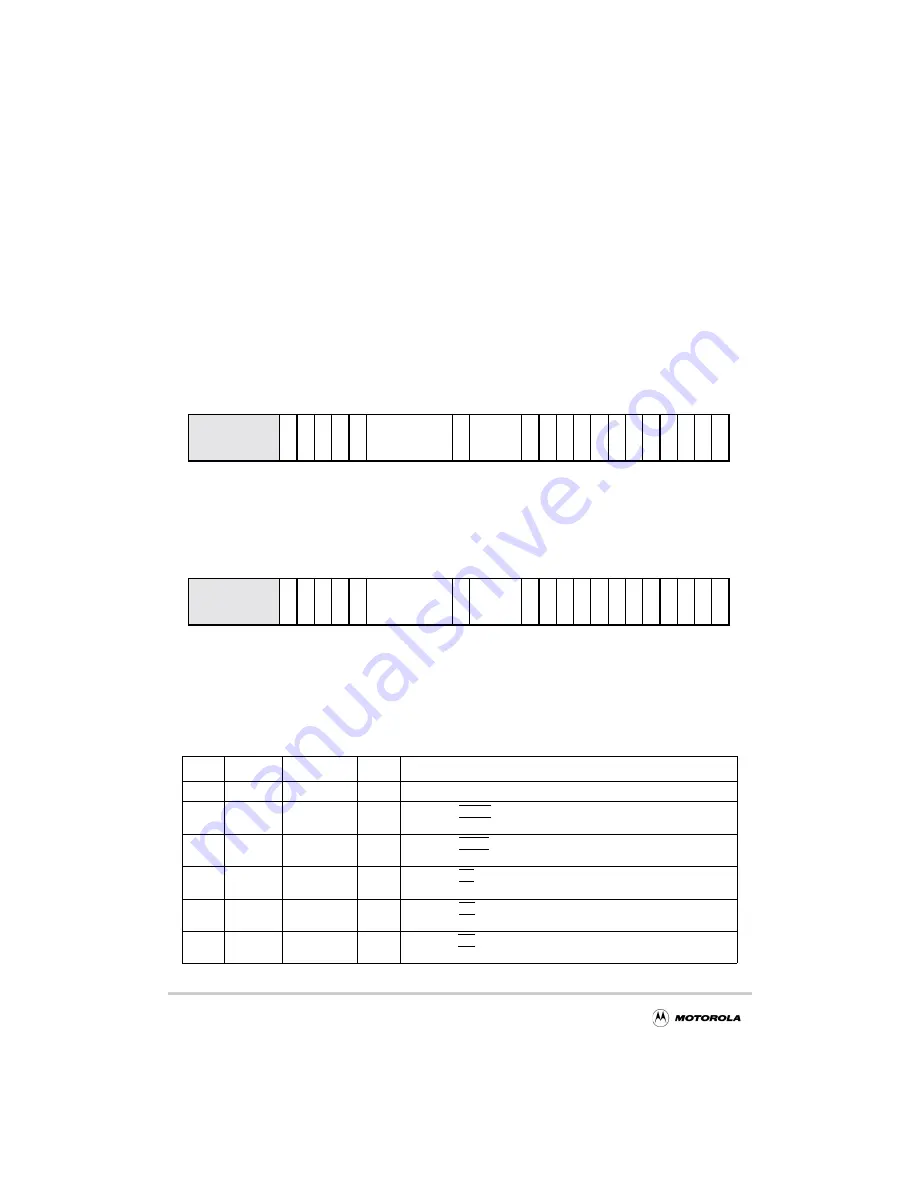

16.2.2 Watchpoint Trigger Registers

Watchpoint triggers are set based on a subset of the peripheral logic bus that includes the

32-bit address bus and 26 control signals. These watchpoints are compared with the values

on the peripheral logic bus on every clock cycle. There are separate sets of trigger registers

for watchpoints #1 and #2. These registers are read/write and initialized to 0x0000_0000

on reset.

Figure 16-2 and Figure 16-3 show the format of the watchpoint #1 and watchpoint #2

control trigger registers (WP1_CNTL_TRIG and WP2_CNTL_TRIG). Note that the

format of these two registers is identical, but they are shown separately to emphasize that

their location is at different offsets.

Figure 16-2. Watchpoint #1 Control Trigger Register (WP1_CNTL_TRIG)—

Offsets 0xF_F018, 0xF18

Figure 16-3. Watchpoint #1 Control Trigger Register (WP1_CNTL_TRIG)—

Offsets 0xF_F030, 0xF30

Table 16-3 shows the bit definitions for WP1_CNTL_TRIG and WP2_CNTL_TRIG.

Table 16-3. Watchpoint Control Trigger Register Bit Field Definitions

Bits

Name

Reset Value

R/W

Description

31–26

—

0b000_000

R

Reserved

25

QREQ_

0

R/W

0 Trigger if QREQ asserted on peripheral logic bus

1 Trigger if QREQ negated

24

QACK_

0

R/W

0 Trigger if QACK asserted on peripheral logic bus

1 Trigger if QACK negated

23

BR_

0

RW

0 Trigger if BR asserted on peripheral logic bus

1 Trigger if BR negated

22

BG_

0

RW

0 Trigger if BG asserted on peripheral logic bus

1 Trigger if BG negated

21

TS_

0

R/W

0 Trigger if TS asserted on peripheral logic bus

1 Trigger if TS negated

0000_00

QREQ_

QA

CK_

BR_

BG_

TS_

TT0[0:4]

TBST_

TSIZ[0:2]

GBL_

CI_

WT_

TC0

TC1

AA

CK_

AR

TR

Y_

DBG_

TA

_

TEA_

INT_

MCP_

31

26 25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0000_00

QREQ_

QA

CK_

BR_

BG_

TS_

TT0[0:4]

TBST_

TSIZ[0:2]

GBL_

CI_

WT_

TC0

TC1

AA

CK_

AR

TR

Y_

DBG_

TA

_

TEA_

INT_

MCP_

31

26 25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...