Chapter 4. Configuration Registers

4-37

Error Handling Registers

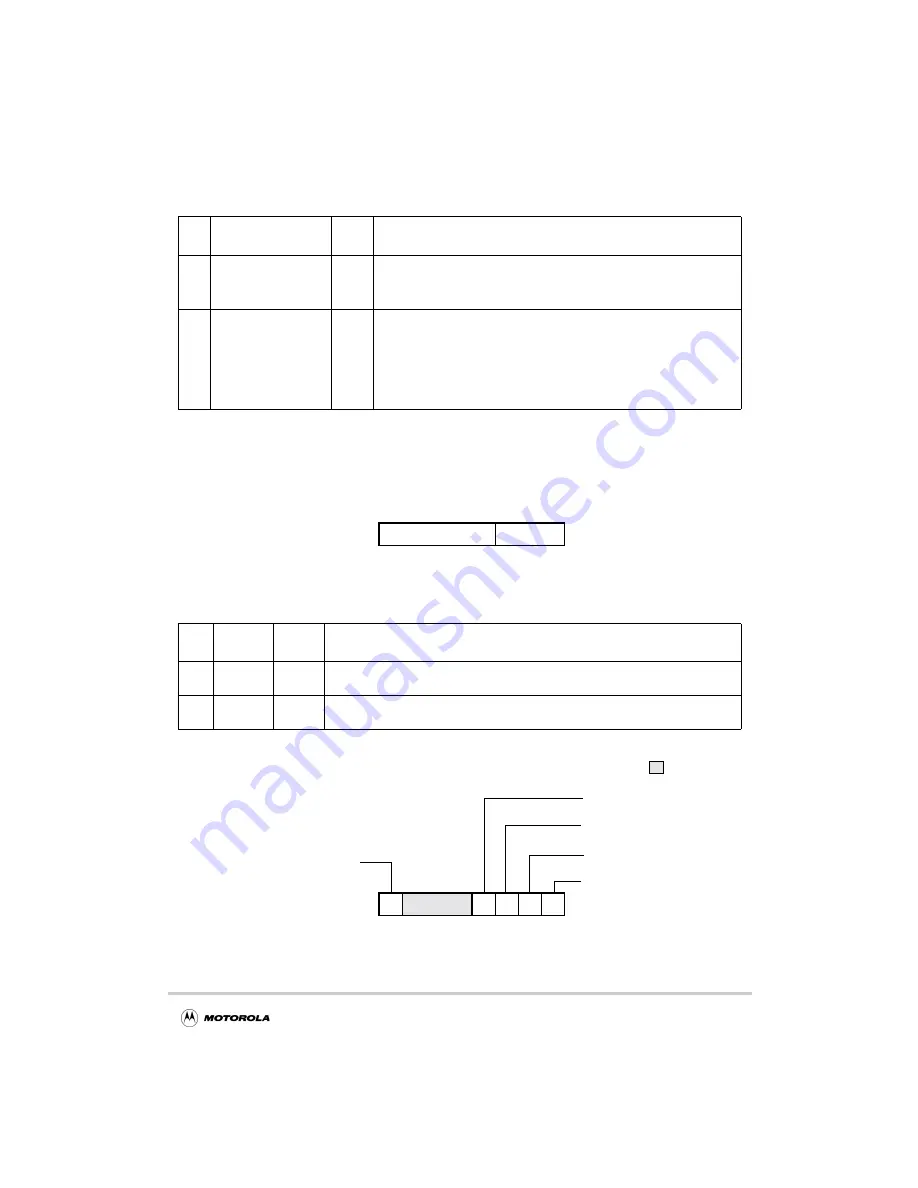

The processor bus error status register (BESR) latches the state of the internal processor

address attributes when an internal bus error is detected. This information then can be used

by error handling software. Figure 4-23 shows the bits of the processor bus error status

register and Table 4-32 provides a detailed description of the bit settings.

Figure 4-23. Internal Processor Bus Error Status Register—0xC3

U

Figure 4-24 shows the enable bits for ErrEnR2.

Figure 4-24. Error Enabling Register 2 (ErrEnR2)—0xC4

2

Memory read parity

error/ECC single-bit

error trigger exceeded

0

Memory read parity error/ECC single-bit error trigger exceeded

0 No error detected

1 Parity error detected or ECC single-bit error trigger exceeded

1–0

Unsupported

processor transaction

00

Unsupported processor transaction

00 No error detected

01 Unsupported transfer attributes. Refer to Chapter 13, “Error Handling,”

for more details.

10 Reserved

11 Reserved

Table 4-32. Bit Settings for Internal Processor Bus Error Status Register—0xC3

Bits

Name

Reset

Value

Description

7–3

TT[0:4]

0000_0

These bits maintain a copy of TT[0:4]. When a processor bus error is detected, these

bits are latched until all error flags are cleared.

2–0

TSIZ[0:2]

000

These bits maintain a copy of TSIZ[0:2]. When a processor bus error is detected,

these bits are latched until all error flags are cleared.

Table 4-31. Bit Settings for Error Detection Register 1 (ErrDR1)—0xC1 (Continued)

Bits

Name

Reset

Value

Description

TT[0:4]

TSIZ[0:2]

7

3

2

0

Reserved

Flash ROM Write Error

0 0 0

7

6

4

3

2

1

0

Processor/Memory Write

PCI Address Parity Error Enable

PCI Received Target Abort

Enable

ECC Multibit Error Enable

Parity Error Enable

Error Enable

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...