MMC2001

UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER MODULE

MOTOROLA

REFERENCE MANUAL

11-15

RTSD — RTS Delta

When set, this bit indicates that the RTS pin changed state. It generates a maskable

interrupt. In STOP mode, RTS assertion sets this bit to wake the CPU. The current

state of the RTS pin is available in the RTSS bit. The RTSD interrupt is cleared by

writing a one to this bit.

0 =

RTS pin did not change state since last cleared

1 =

RTS pin changed state

At reset, this bit is cleared to zero.

11.4.7 UART Test Register (UTS)

The UART test register is a read/write register. Unimplemented bits always return

zero when read. This register contains miscellaneous bits to control test features of

the UART block.

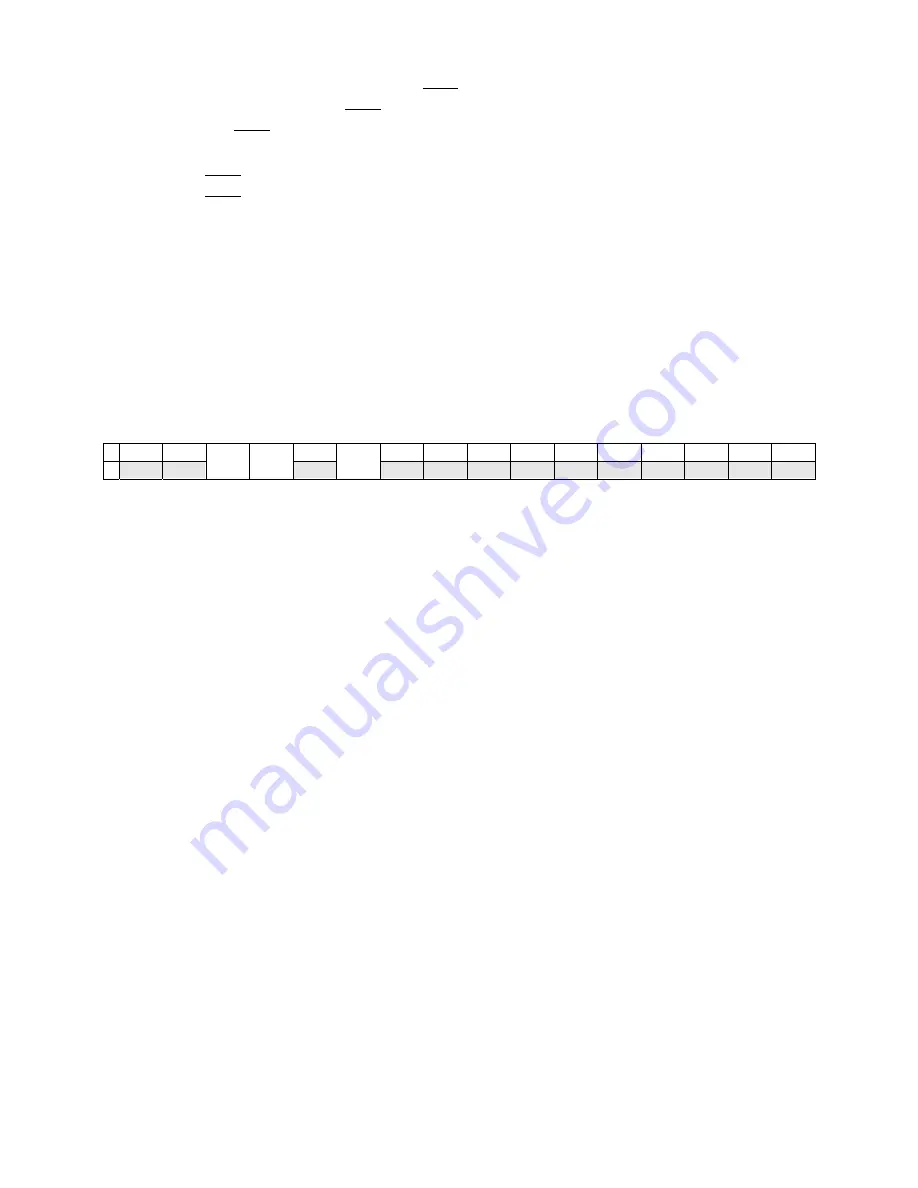

Figure 11-8 UART Test Register

FRC PERR — Force Parity Error

When set, this bit forces the transmitter to generate a parity error if parity is enabled.

This bit is provided for system debugging.

0 =

Generate normal parity

1 =

Generate inverted parity (error)

At reset, this bit is cleared to zero.

LOOP — Loop TX and RX for Test

This bit controls loopback for test purposes. While this bit is high, the receiver input is

internally connected to the transmitter and ignores the RxD pin. The transmitter is

unaffected by this bit. This loopback operates to connect the data on the TxD pin

directly to the voting logic. If infrared mode is enabled (IR_EN is active), the effect of

activating this bit is to put an IR-formatted bit stream into the voting logic, which will

yield odd results. Do not use this loopback if IR_EN is active.

0 =

Normal receiver operation

1 =

Internal connect transmitter output to receiver input

At reset, this bit is cleared to zero.

LOOP IR — Loop TX and RX for IR Test

This bit controls a loopback from transmitter to receiver in the infrared interface.

0 =

No IR loop

1 =

Connect IR transmit to IR receiver

At reset, this bit is cleared to zero.

U0TS — UART0 Test Register

10009088

U1TS — UART1 Test Register

1000A088

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

FRC

PERR

LOOP

0

LOOP

IR

0

0

0

0

0

0

0

0

0

0

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Freescale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc.

..