4

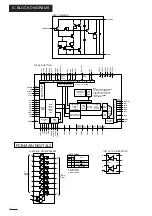

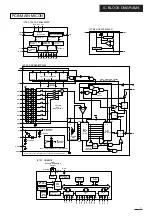

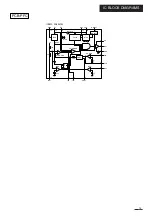

IC2A1 NJM431U

1

REFERENCE

3

CATHODE

2

ANODE

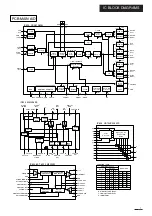

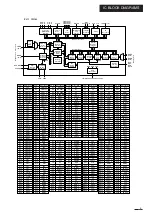

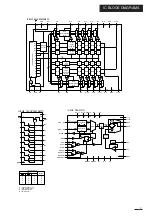

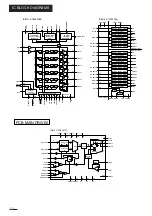

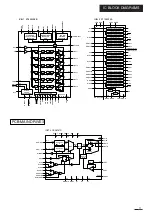

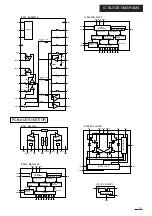

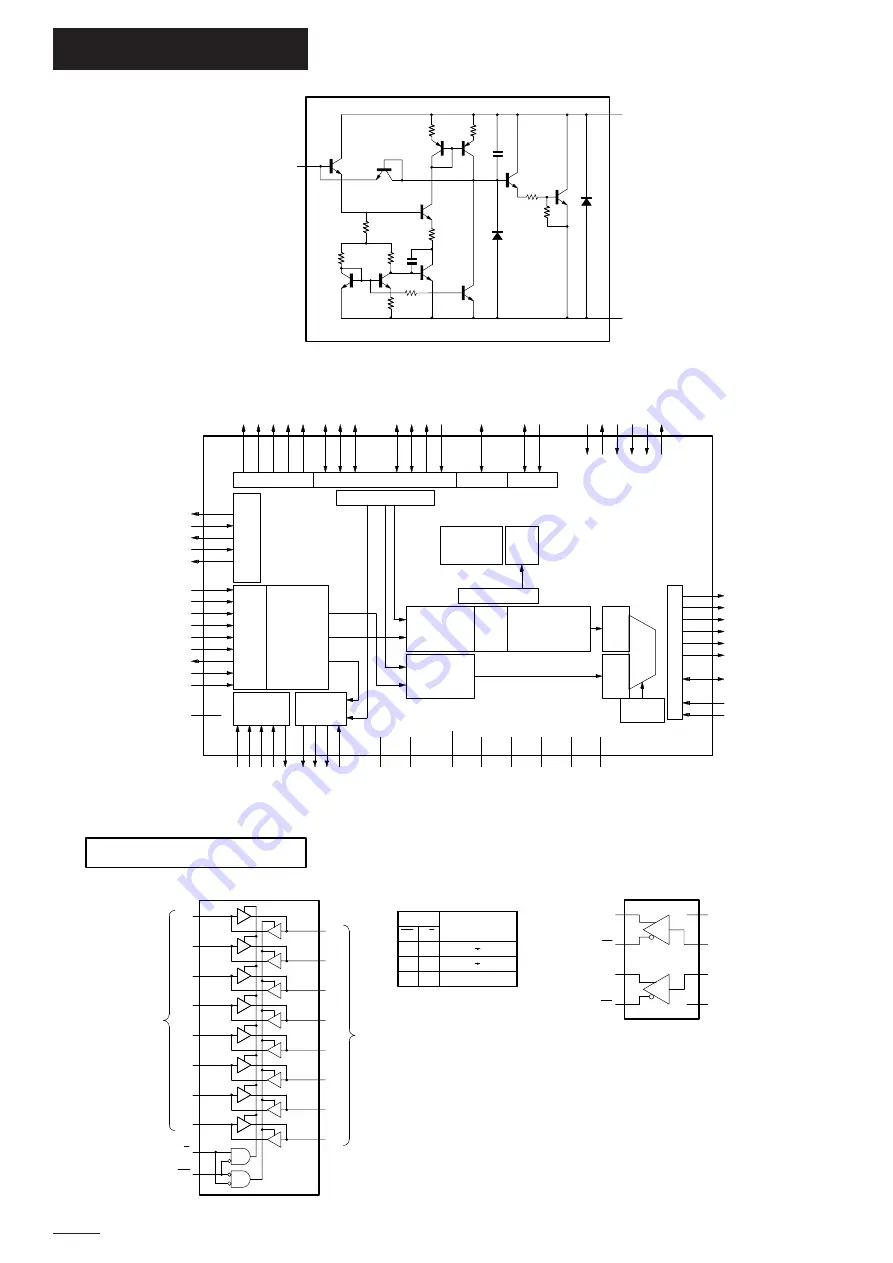

IC2A2 SAA7114H

RT out

IPD[7:0]

eXpansion port pin mapping

I/O control

IIC

X port I/O formatting

programming

Register

array

A/B

Reg.

MUX

event controller

FIR-Prefilter

Perscaler

and

scaler BCS

Line

FIFO

buffer

Vertical

Scaling

Horizonal

Fine

(Phase)

Scaling

general purpose

VBI data sllcer

video

FIFO

text

FIFO

Note:

The pins RTCO and ALRCLK

are used for configuration

of the IIC Interface and the

definition of the crystal osc.

frequency at RESET

(pin strapping)

chroma of 16 bit input

28 29 36 34 35

94 95 81,82,

84-87,

89,90,

92 91 96 80

64-67,

69-72,

32 31

Image port pin mapping

32

to

8(16)

MUX

video/text

arbiter

54-57,

59-62

46

53

52

48

49

45

42

47

clock generation and

power on control

30

27

4

7

6

analog

dual

ADC

digital

decoder

with

adaptive

comb

filter

12

10

22

19

13

20

18

16

14

audio

clock

ganeration

37 40 39 41

boundary

scan

test

98 99 3 2

97

78 77 74 73 44

79

5

8

51,75

83,93

23

88

76,100 24

58,68,

33,43,

1,25,

11,17, 38,63, 26,50, 9,15,

IDQ

IGPH

IGPV

IGP0

IGP1

ICLK

ITRDY

ITRI

RESON

CE

XTOUT

XTALI

XTAL

AI11

AI12

AI21

AI22

AI23

AI24

AOUT

AI1D

AI2D

21

AGND

TRSTN

TCK

TMS

TDI

TDO

AMCLK

ALRCLK

ASCLK

AXMCLK

VXDD

VXSS

VDDI

VDDE

VDDA

VSSI

VSSE

VSSA

LLC

LLC2

RTCO

RTS0

RTS1

XCLK

XDQ

XPD[7:0]

XRH

XRV

XRDY

XTRI

HPD[7:0]

SDA

SCL

TEST5

TEST4

TEST3

TEST2

TEST1

TEST0

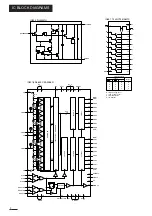

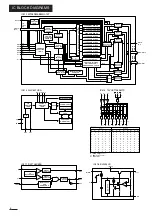

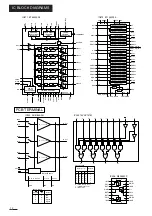

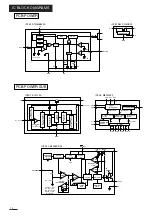

IC411,419 AZ10ELT22D

1

2

8

7

3

4

5

6

PECL

TTL

Q0

Q0

Q1

Q1

GND

D1

D0

V

CC

IC410,416 HD74LVC245AT

2

3

4

5

6

7

8

9

1

19

11

12

13

14

15

16

17

18

A0

A1

A2

A3

A4

A5

A6

A7

T/R

OE

B7

B6

B5

B4

B3

B2

B1

B0

A

DATA

PORT

B

DATA

PORT

B DATA A DATA

A DATA B DATA

ISOLATION

T/R

OE

L

L

L

H

H

X

IN

OUT

H

L

X

: HIGH LEVEL

: LOW LEVEL

: DON'T CARE

TRUTH TABLE

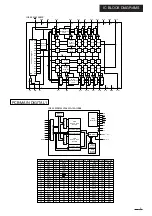

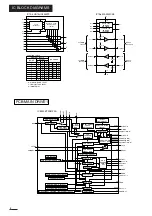

PCB-MAIN DIGITAL2

IC BLOCK DIAGRAMS

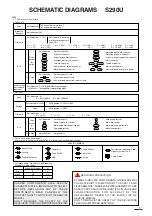

Summary of Contents for S290U

Page 83: ...16 ...

Page 180: ...113 SYMBOL NO ADDRESS X7A1 A 3 PCB MAIN COMPONENT SIDE ...

Page 188: ...121 ...