MAX32600 User’s Guide

System Clock, Timers/Counters, Watchdog Timers and Real Time Clock

10.1 System Clock

This register field must be left at its default value for proper operation.

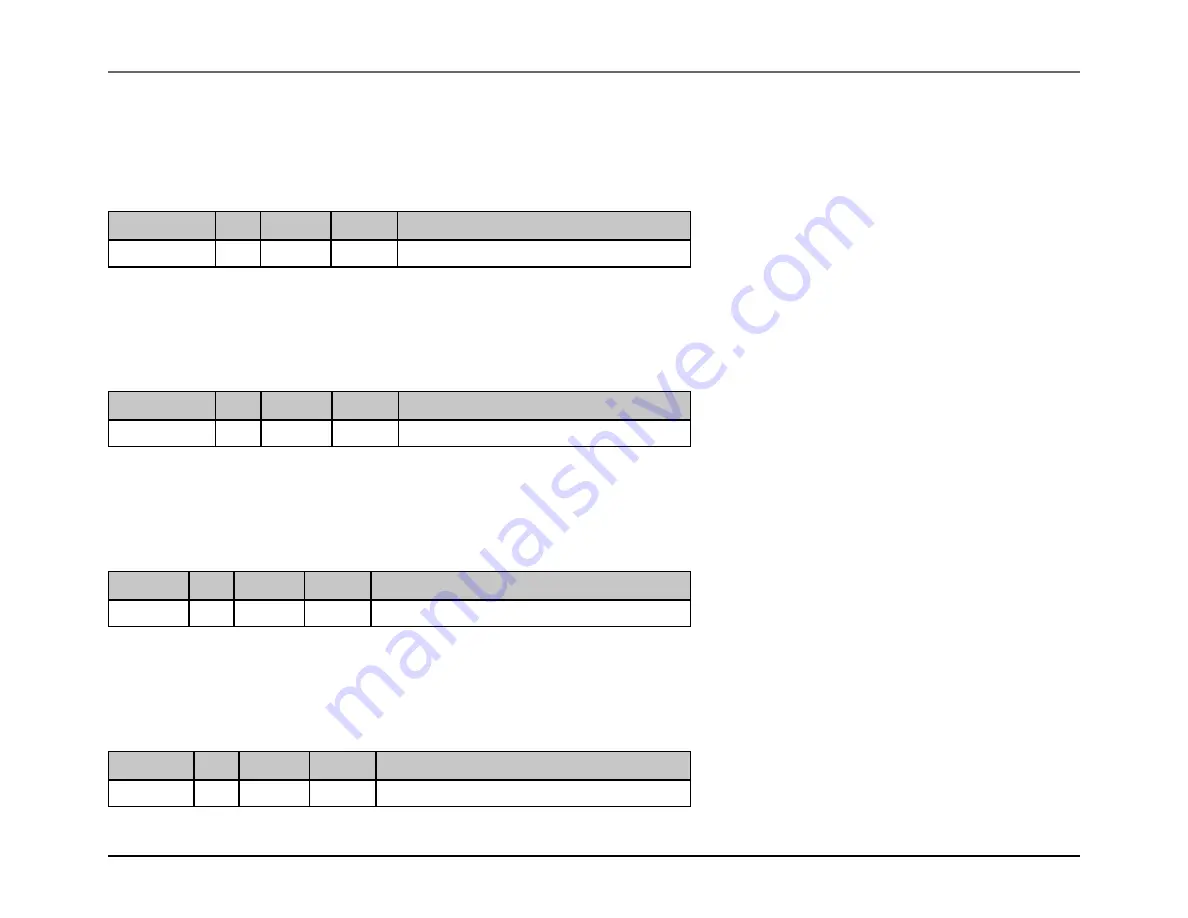

CLKMAN_CLK_CONFIG.hfx_gm_adjust

Field

Bits

Default

Access

Description

hfx_gm_adjust

8:4

no effect

R/W

HFX GM Adjust

GM Adjust for Crystal Oscillator Amp

CLKMAN_CLK_CONFIG.hfx_dc_control

Field

Bits

Default

Access

Description

hfx_dc_control

11:9

no effect

R/W

HFX DC Control

Duty Cycle Control for Crystal Oscillator Amp

CLKMAN_CLK_CONFIG.pll_enable

Field

Bits

Default

Access

Description

pll_enable

12

no effect

R/W

PLL Enable

Enable Phase Lock Loop clock source generator

CLKMAN_CLK_CONFIG.pll_reset_n

Field

Bits

Default

Access

Description

pll_reset_n

13

no effect

R/W

PLL ResetN

Rev.1.3 April 2015

Maxim Integrated

Page 513