MAX32600 User’s Guide

Communication Peripherals

7.2 SPI

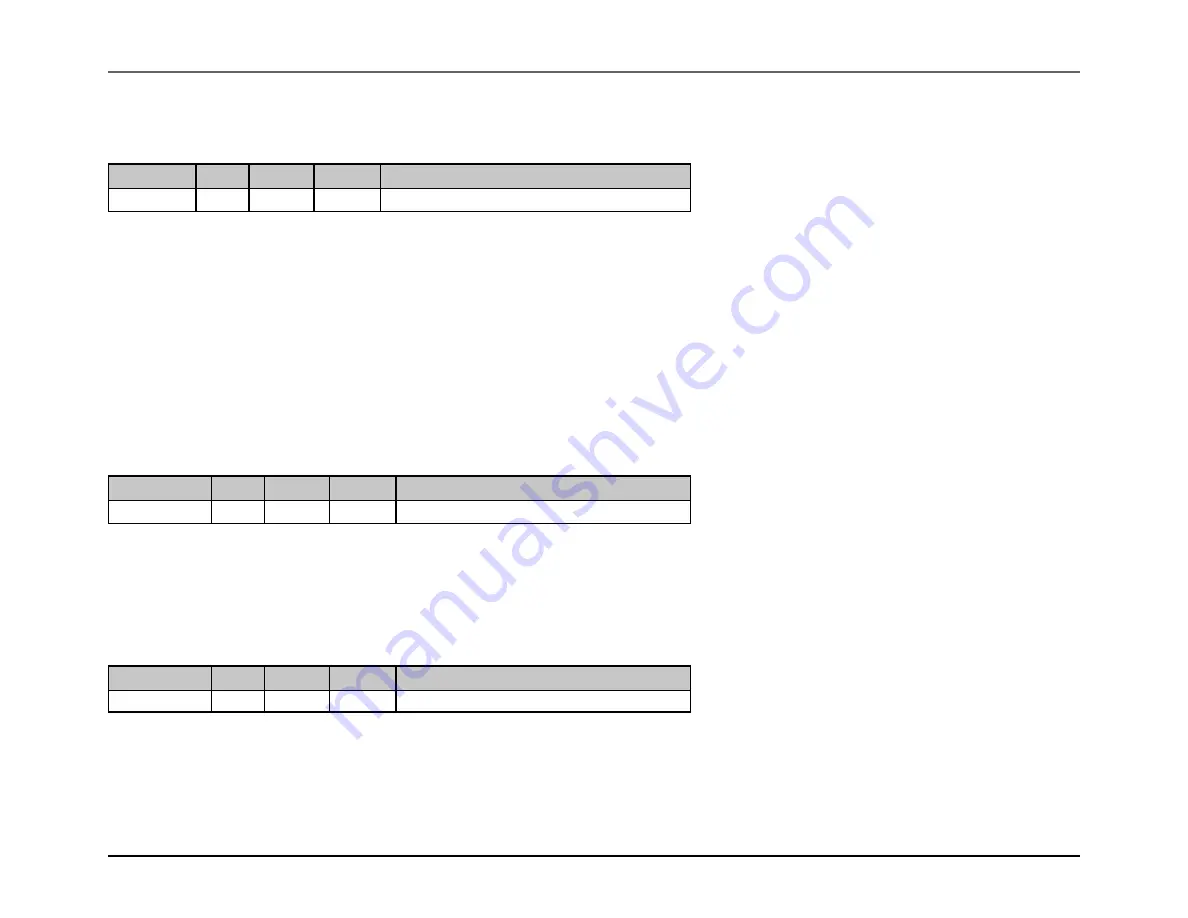

SPIn_MSTR_CFG.inact_delay

Field

Bits

Default

Access

Description

inact_delay

19:18

00b

R/W

SS Inactive Timing

Controls the delay between deassertion of SS at the end of a transaction and reassertion of SS to begin the next transaction, for back-to-back SPI transactions.

• 00b: 0 system clocks

• 01b: 2 system clocks

• 10b: 4 system clocks

• 11b: 8 system clocks

SPIn_MSTR_CFG.alt_sck_hi_clk

Field

Bits

Default

Access

Description

alt_sck_hi_clk

23:20

0000b

R/W

Alt SCK High Clocks

Number of system clocks SCK will be in the active state (determined by clock polarity setting), when alternate timing generation is enabled. If this is set to 0, "Fast

Mode" is enabled, in which SCK is a gated version of the system clock.

SPIn_MSTR_CFG.alt_sck_lo_clk

Field

Bits

Default

Access

Description

alt_sck_lo_clk

27:24

0000b

R/W

Alt SCK Low Clocks

Number of system clocks SCK will be in the inactive state (determined by clock polarity setting), when alternate timing generation is enabled. If this is set to 0, "Fast

Mode" is enabled, in which SCK is a gated version of the system clock.

Rev.1.3 April 2015

Maxim Integrated

Page 273