69rlq62d-f714peg4 * Memec (Headquar

ter

s) - Unique

Tec

h,

Insight,

Impact

MAR

VELL CONFIDENTIAL,

UNDER ND

A# 12101050

69rlq62d-f714peg4 * Memec (Headquar

ter

s) - Unique

Tec

h,

Insight,

Impact

MAR

VELL CONFIDENTIAL,

UNDER ND

A# 12101050

69r

lq62d-f714peg4 * Memec (Headquar

ters) - Unique

T

ech, Insight, Impact * UNDER ND

A# 12101050

MAR

VELL CONFIDENTIAL - UNA

UTHORIZED DISTRIB

UTION OR USE STRICTL

Y PR

OHIBITED

PXA300 Processor and PXA310 Processor

Vol. I: System and Timer Configuration Developers Manual

Doc. No. MV-TBD-00 Rev. A

CONFIDENTIAL

Copyright © 12/13/06 Marvell

Page 324

Document Classification: Proprietary Information

December 13, 2006

Not approved by Document Control. For review only.

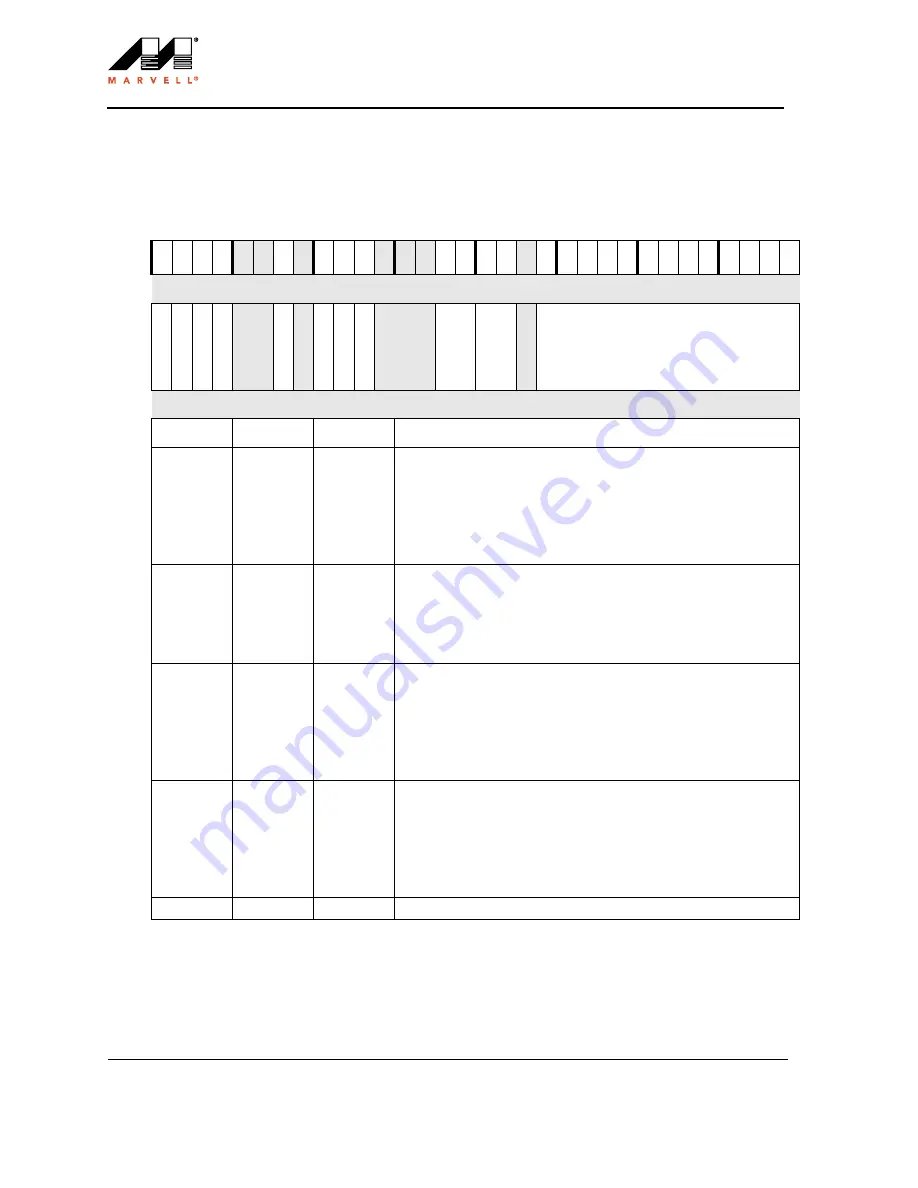

Table 11-13. DCMD0–31 Bit Definitions (Sheet 1 of 4)

Physical Address

0x4000_02xC–0x4000_03xC

DCMD0–DCMD31

DMA Controller

User

Settings

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

IN

CS

RCAD

DR

IN

CT

RGAD

DR

FLOWS

RC

FLOWT

RG

Reserved

CMP

E

N

Reserved

ADDRM

O

D

E

ST

A

R

T

IR

QE

N

E

N

DI

RQE

N

Reserved

SIZE

WI

D

T

H

Reserved

LEN

Reset

0

0

0

0

?

?

0

0

0

0

0

?

?

?

0

0

0

0

?

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Access

Name

Description

31

R/W

INCSRCADDR

Source address increment

If the source address is an internal peripheral FIFO address or external I/O

address, the address is not incremented on each successive access. In

these cases, DCMDx[INCSRCADDR] must be cleared.

0 = Do not increment source address

1 = Increment source address

30

R/W

INCTRGADDR

Target address increment

If the target address is an internal peripheral FIFO address or external I/O

address, the address is not incremented on each successive accesses. In

these cases, DCMDx[INCTRGADDR] must be cleared.

0 = Do not increment target address

1 = Increment target address

29

R/W

FLOWSRC

Source flow control

The flow control of the source bit must be set if the source is an on-chip

peripheral or external companion chip.

Setting both the FLOWSRC and FLOWTRG bits causes unpredictable

behavior.

0 = Do not wait for request signals associated with this channel.

1 = Wait for a request signal before initiating the data transfer

28

R/W

FLOWTRG

Target flow control

The flow control of the target bit must be set if the target is an on-chip

peripheral or external companion chip.

Setting both the FLOWSRC and FLOWTRG bits causes unpredictable

behavior.

0 = Do not wait for request signals associated with this channel.

1 = Wait for a request signal before initiating the data transfer

27:26

—

Reserved

Reserved