4-12

Register Descriptions

4.2.3 Register 14

RES

Reserved

7

This bit is reserved.

START_MEASUREMENT

R/W 6

A transition from 0-to-1 starts a measurement of the byte

clock connected to the ICLK input. MEASUREMENT_

DONE in status register (13) indicates the end of the

measurement. The reset value is 0.

ENABLE_NCO_ LOOP

R/W 5

Setting this bit allows a step update in the NCO loop

based on the FIFO fullness. The REF_DUR parameter

can adjust the update frequency. The reset value is 0.

MASK_NCO_IRQ

R/W 4

Setting this bit enables the interrupt for the

MEASUREMENT_DONE event. Even in the case of a

disabled interrupt, the status is indicated correctly. The

reset value is 0.

AUTO_ACQUISITION_ON

R/W 3

A 1-to-0 transition in this bit starts an internal procedure

to regulate the NCO frequency. The reset value is 0.

Setting this bit to 1 activates the autoacquisition mode.

MASK_ACQ_IRQ

R/W 2

If this bit is 1, a transition from 1 to 0 in the

AUTO_ACQUI_RUNNING bit of register 13 causes an

interrupt. The interrupt is visible in the NCO_EVENT bit

of register 12 and clears upon the reading of register 13.

The reset value is 0.

EN_PHASE_LOOP

R/W 1

Setting this bit enables the phase acquisition loop, after

Autofrequency Acquisition is completed in the NCO mode

of operation. The reset value is 0.

7

6

5

4

3

2

1

0

RES

START_

MEASURE-

MENT

ENABLE_

NCO_LOOP

MASK_NCO_

IRQ

AUTO_

ACUISITION

_ON

MASK_ACQ_

IRQ

EN_PHASE_

LOOP

FIFO_INT

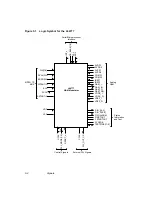

Summary of Contents for L64777

Page 1: ...L64777 DVB QAM Modulator Order Number I14031 A Technical Manual June 2000...

Page 10: ...x Contents...

Page 14: ...1 4 Introduction...

Page 90: ...5 10 Signals...

Page 110: ...A 8 Programming the L64777 in Serial Host Interface Mode...

Page 116: ...C 2 Monitoring Device Internal Signals...

Page 124: ......