C6000 Debugger | 31

©

1989-2022

Lauterbach

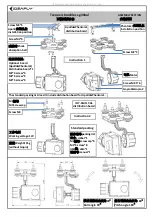

<parameters> describing debug and trace “Components”

On the

Components

tab in the

SYStem.CONFIG.state

window, you can comfortably add the debug and

trace components your chip includes and which you intend to use with the debugger’s help.

Each configuration can be done by a command in a script file as well. Then you do not need to enter

everything again on the next debug session. If you press the button with the three dots you get the

corresponding command in the command line where you can view and maybe copy it into a script file.