Intel® Server System M50CYP1UR Family System Integration and Service Guide

104

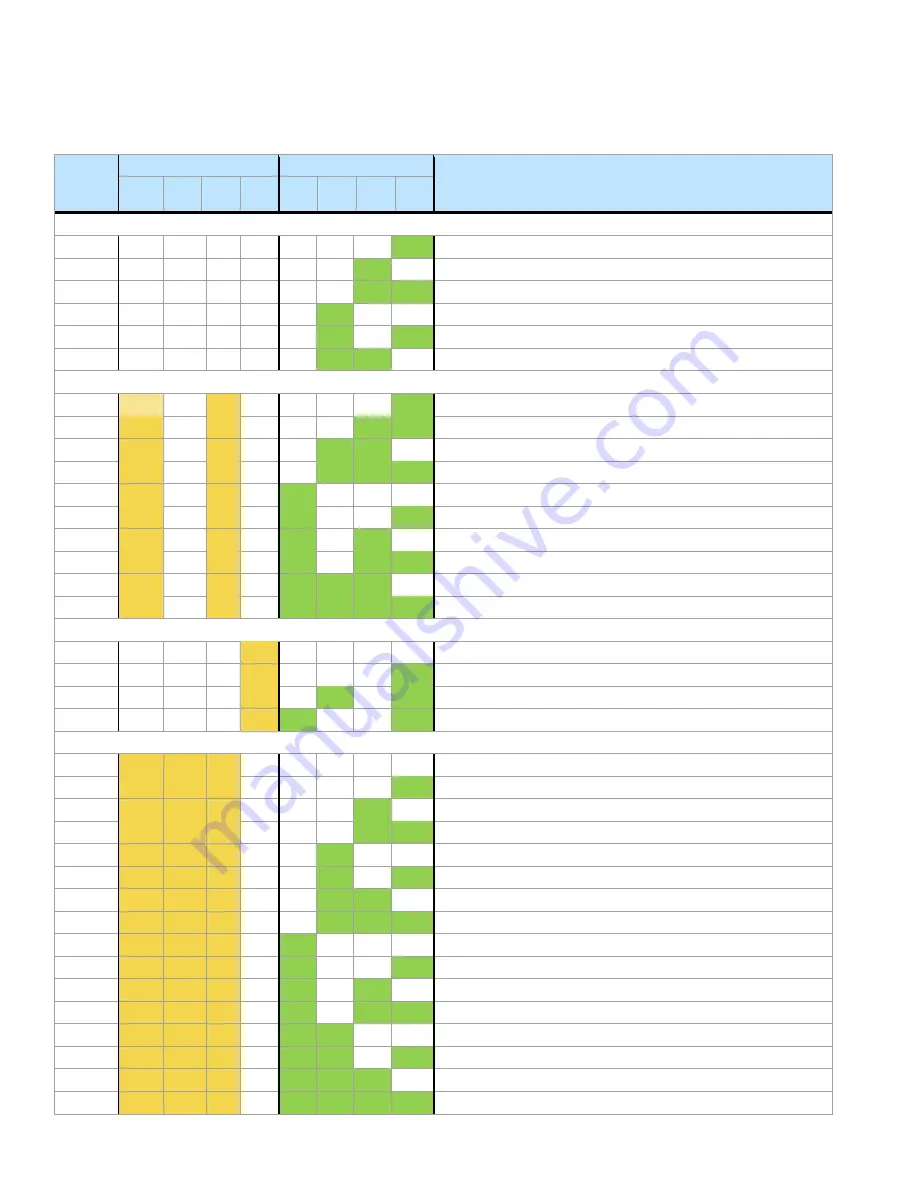

E.2 BIOS POST Progress Codes

The following table provides a list of all POST progress codes.

Table 11. POST Progress Codes

Post

Code

(Hex)

Upper Nibble

Lower Nibble

Description

8h

4h

2h

1h

8h

4h

2h

1h

SEC Phase

01

0

0

0

0

0

0

0

1

First POST code after CPU reset

02

0

0

0

0

0

0

1

0

Microcode load begin

03

0

0

0

0

0

0

1

1

CRAM initialization begin

04

0

0

0

0

0

1

0

0

PEI Cache When Disabled

05

0

0

0

0

0

1

0

1

SEC Core At Power On Begin.

06

0

0

0

0

0

1

1

0

Early CPU initialization during SEC Phase.

UPI RC (Fully leverage without platform change)

A1

1

0

1

0

0

0

0

1

Collect info such as SBSP, boot mode, reset type, etc.

A3

1

0

1

0

0

0

1

1

Setup minimum path between SBSP and other sockets

A6

1

0

1

0

0

1

1

0

Sync up with PBSPs

A7

1

0

1

0

0

1

1

1

Topology discovery and route calculation

A8

1

0

1

0

1

0

0

0

Program final route

A9

1

0

1

0

1

0

0

1

Program final IO SAD setting

AA

1

0

1

0

1

0

1

0

Protocol layer and other uncore settings

AB

1

0

1

0

1

0

1

1

Transition links to full speed operation

AE

1

0

1

0

1

1

1

0

Coherency settings

AF

1

0

1

0

1

1

1

1

KTI initialization done

PEI Phase

10

0

0

0

1

0

0

0

0

PEI Core

11

0

0

0

1

0

0

0

1

CPU PEIM

15

0

0

0

1

0

1

0

1

Platform Type Init

19

0

0

0

1

1

0

0

1

Platform PEIM Init

Integrated I/O Progress Codes

E0

1

1

1

0

0

0

0

0

Integrated I/O Early Init Entry

E1

1

1

1

0

0

0

0

1

Integrated I/O Pre-link Training

E2

1

1

1

0

0

1

0

Integrated I/O EQ Programming

E3

1

1

1

0

0

0

1

1

Integrated I/O Link Training

E4

1

1

1

0

0

1

0

0

Internal Use

E5

1

1

1

0

0

1

0

1

Integrated I/O Early Init Exit

E6

1

1

1

0

0

1

1

0

Integrated I/O Late Init Entry

E7

1

1

1

0

0

1

1

1

Integrated I/O PCIe Ports Init

E8

1

1

1

0

1

0

0

0

Integrated I/O IOAPIC init

E9

1

1

1

0

1

0

0

1

Integrated I/O VTD Init

EA

1

1

1

0

1

0

1

0

Integrated I/O IOAT Init

EB

1

1

1

0

1

0

1

1

Integrated I/O DXF Init

EC

1

1

1

0

1

1

0

0

Integrated I/O NTB Init

ED

1

1

1

0

1

1

0

1

Integrated I/O Security Init

EE

1

1

1

0

1

1

1

0

Integrated I/O Late Init Exit

EF

1

1

1

0

1

1

1

1

Integrated I/O ready to boot