IDT Hot-Plug and Hot-Swap

PES32NT24xG2 User Manual

11 - 4

January 30, 2013

Notes

The switch utilizes external SMBus/I

2

C-bus I/O expanders connected to the master SMBus interface for

hot-plug related signals associated with downstream switch ports. See section I/O Expanders on page 12-

11 for details on the operation of the I/O expanders and for the mapping of hot-plug signals to I/O expander

inputs and outputs.

SMBus I/O expander transactions are automatically initiated when the state of a hot-plug input signal

changes or a new value needs to be driven on a hot-plug output signal. When an I/O Expander is initialized

(i.e., the IOEXPADDR field in the IOEXPADDR[4:0] registers is written), the hot-plug controller for the corre-

sponding port initiates an SMBus access to configure the I/O Expander and updates the status bits in the

PCI Express Slot Status (PCIESSTS) register. During this initial access, the Presence Detect Changed

(PDC) and MRL Sensor Changed (MRLSC) bits in the hot-plug port’s PCIESSTS register are not set, since

this access is used to determine the initial state of the I/O Expander signals.

The switch supports presence detect signaling via assertion of the Presence Detect Input signal in the

external I/O Expander module and through “in-band” presence detect (i.e., the port’s PHY detects the pres-

ence of a link-partner). The Presence Detect Control (PDETECT) field in the Hot-Plug Configuration Control

(HPCFGCTL) register may be used to control the mechanism used for presence detect. The settings in the

HPCFGCTL register are globally applied to all hot-plug ports in the switch.

Since the polarity of hot-plug signals has been defined differently in various specifications, each hot plug

signal except PxRSTN has a corresponding control bit in the Hot-Plug Configuration Control (HPCFGCTL)

that allows the polarity of that signal to be inverted. Inversion affects the corresponding signal in all ports.

When a one is written to the Electromechanical Interlock Control (EIC) bit in the port’s PCI Express Slot

Control (PCIESCTL) register, then the PxILOCKP signal is pulsed for a length greater than 100 ms and less

than 150 ms (i.e., it transitions from negated to asserted, maintains an asserted state for 100 to 150 ms,

and then transitions back to negated). When the Toggle Electromechanical Interlock Control (TEMICTL) bit

in the HPCFGCTL register is set, writing a one to the EIC bit inverts the state of the PxILOCKP signal.

When the MRL Automatic Power Off (MRLPWROFF) bit is set in the HPCFGCTL register and the

Manual Retention Latch Sensor Present (MRLP) bit is set in the PCI Express Slot Capability (PCIESCAP)

register, then power to the slot is automatically turned off when the MRL sensor indicates that the MRL is

open. This occurs regardless of the state of the Power Controller Control (PCC) bit in the hot-plug port’s

PCIESCTL register.

The state of a port’s Power Fault (PxPFN) input is not latched. For proper operation the system designer

should ensure that once the PxPFN signal is asserted, it remains asserted until the power enable (PxPEP)

signal is toggled. This is required adapter behavior for the PCI Express ExpressModule form factor.

The default value of hot-plug registers following a switch fundamental reset may be configured via serial

EEPROM initialization. Since hot-plug I/O Expander initialization occurs after serial EEPROM initialization,

the Command Completed (CC) bit is not set in the hot-plug port’s PCIESSTS register as a result of serial

EEPROM initialization.

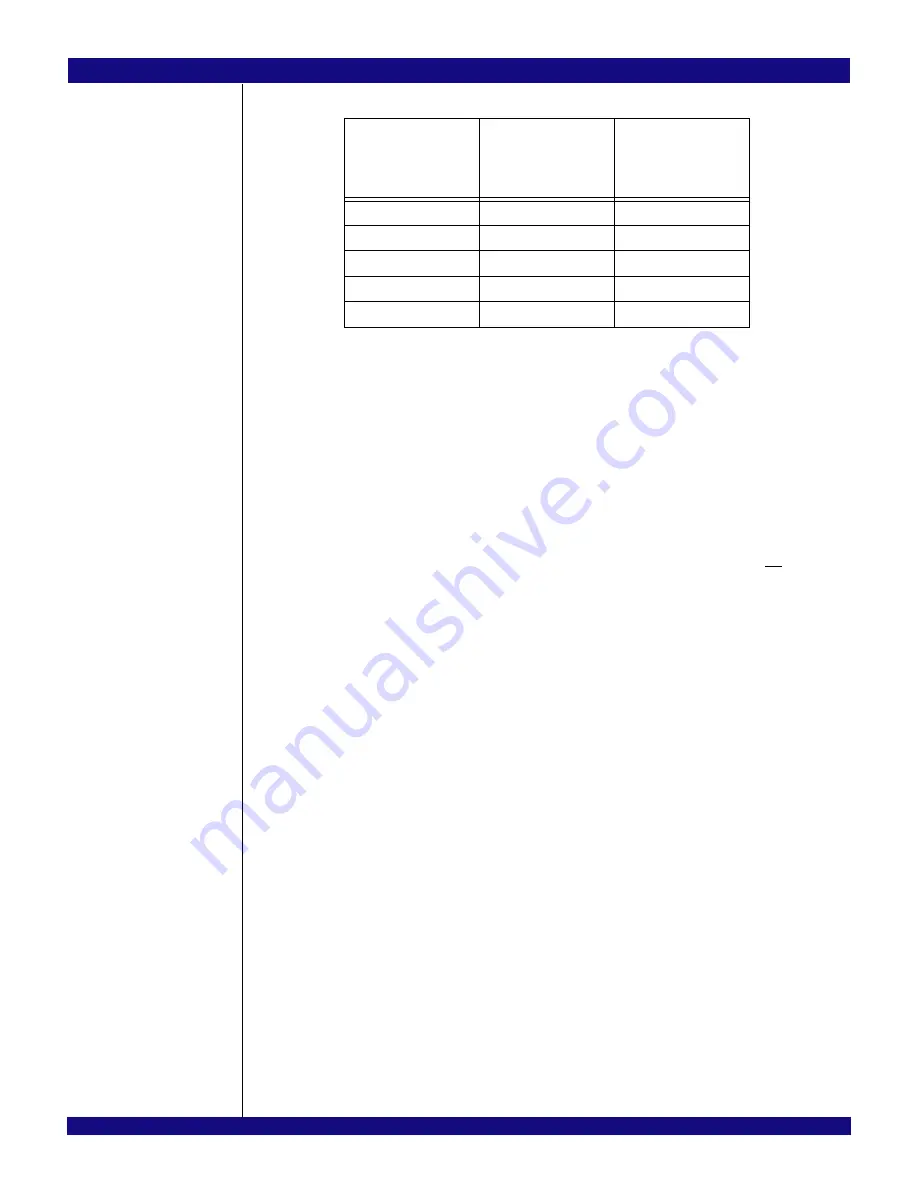

Signal

Negated Output

Value with Non-

Inverted Polarity

(IPXxxx = 0)

Negated Output

Value with

Inverted Polarity

(IPXxxx = 1)

PxAIN

1 (high)

0 (low)

PxILOCKP

0 (low)

1 (high)

PxPEP

0 (low)

1 (high)

PxPIN

1 (high)

0 (low)

PxRSTN

1

1.

PxRSTN signal polarity inversion is not supported.

1 (high)

Not Applicable

Table 11.2 Negated Value of Unused Hot-Plug Output Signals

Summary of Contents for PCI Express 89HPES32NT24xG2

Page 20: ...IDT Table of Contents PES32NT24xG2 User Manual x January 30 2013 Notes...

Page 24: ...IDT List of Tables PES32NT24xG2 User Manual xiv January 30 2013 Notes...

Page 28: ...IDT List of Figures PES32NT24xG2 User Manual xviii January 30 2013 Notes...

Page 56: ...IDT PES32NT24xG2 Device Overview PES32NT24xG2 User Manual 1 20 January 30 2013 Notes...

Page 100: ...IDT Switch Core PES32NT24xG2 User Manual 4 22 January 30 2013 Notes...

Page 128: ...IDT Failover PES32NT24xG2 User Manual 6 4 January 30 2013 Notes...

Page 148: ...IDT Link Operation PES32NT24xG2 User Manual 7 20 January 30 2013 Notes...

Page 164: ...IDT SerDes PES32NT24xG2 User Manual 8 16 January 30 2013 Notes...

Page 170: ...IDT Power Management PES32NT24xG2 User Manual 9 6 January 30 2013 Notes...

Page 196: ...IDT Transparent Switch Operation PES32NT24xG2 User Manual 10 26 January 30 2013 Notes...

Page 244: ...IDT SMBus Interfaces PES32NT24xG2 User Manual 12 40 January 30 2013 Notes...

Page 247: ...IDT General Purpose I O PES32NT24xG2 User Manual 13 3 January 30 2013 Notes...

Page 248: ...IDT General Purpose I O PES32NT24xG2 User Manual 13 4 January 30 2013 Notes...

Page 330: ...IDT Switch Events PES32NT24xG2 User Manual 16 6 January 30 2013 Notes...

Page 342: ...IDT Multicast PES32NT24xG2 User Manual 17 12 January 30 2013 Notes...

Page 344: ...IDT Temperature Sensor PES32NT24xG2 User Manual 18 2 January 30 2013 Notes...

Page 384: ...IDT Register Organization PES32NT24xG2 User Manual 19 40 January 30 2013...

Page 492: ...IDT Proprietary Port Specific Registers PES32NT24xG2 User Manual 21 44 January 30 2013 Notes...

Page 588: ...IDT NT Endpoint Registers PES32NT24xG2 User Manual 22 96 January 30 2013 Notes...

Page 710: ...IDT JTAG Boundary Scan PES32NT24xG2 User Manual 25 12 January 30 2013 Notes...

Page 743: ...IDT Usage Models PES32NT24xG2 User Manual 26 33 January 30 2013 Notes...

Page 744: ...IDT Usage Models PES32NT24xG2 User Manual 26 34 January 30 2013 Notes...