14. Register Descriptions > PCI Capability Registers

167

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

14.5.7

Secondary Bus Device Mask Register

This register provides a method to support private devices on the PCI bus. The process of converting

Type 1 configuration transactions to Type 0 configuration transactions is modified by the contents of

this register. A configuration transaction that targets a device masked by this register is rerouted to

device 15. Setting this register to all zeros disables device masking.

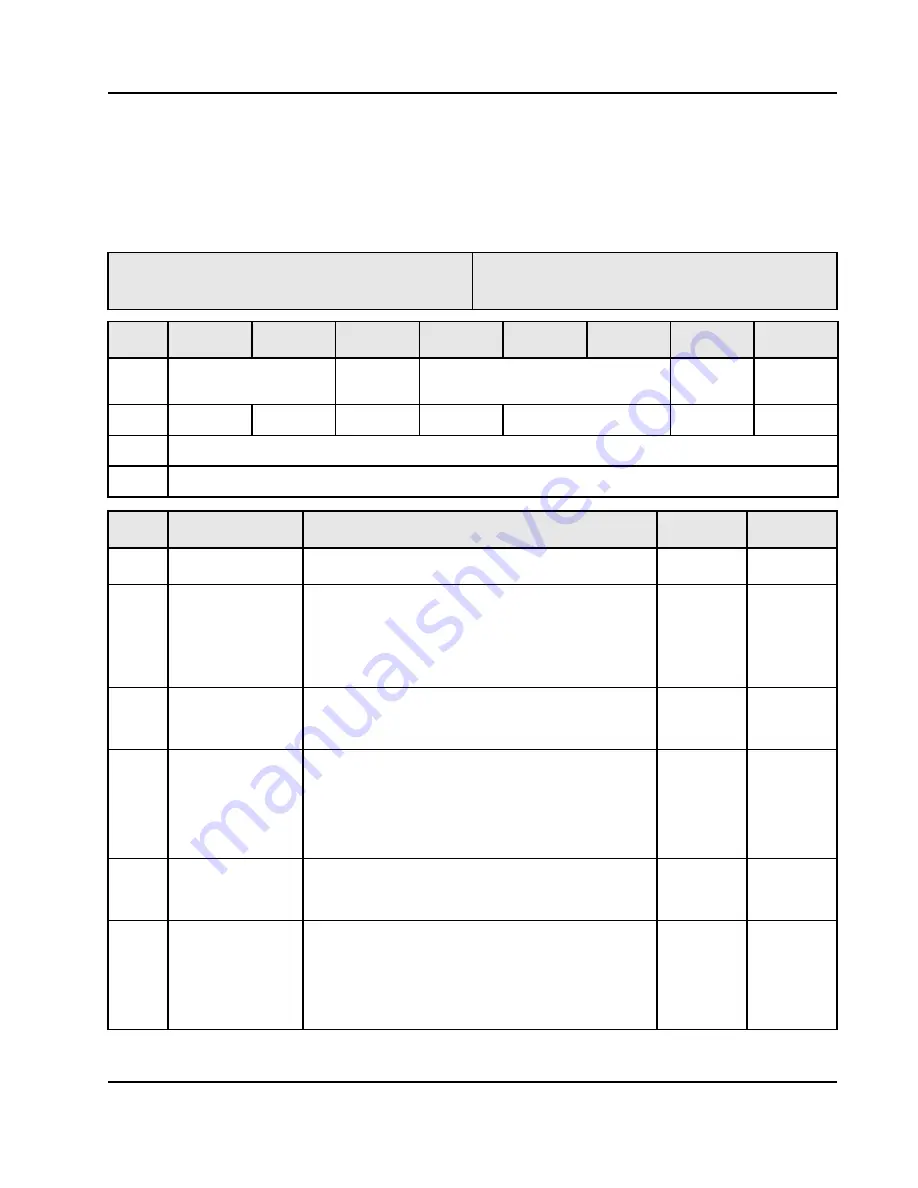

Register name: SBUS_DEVMSK

Reset value: 0x0000_0000

Register offset: 0x0B0

Bits

7

6

5

4

3

2

1

0

31:24

Reserved

DEVMSK_

13

Reserved

DEVMSK_9

Reserved

23:16

DEVMSK_7

DEVMSK_6

DEVMSK_5

DEVMSK_4

Reserved

DEVMSK_1

Reserved

15:08

Reserved

07:00

Reserved

Bits

Name

Description

Type

Reset Value

31:30

Reserved

Reserved

R

0

29

DEVMSK_13

Device Mask 13

0 = Rerouting disabled for device 13.

1 = Block assertion of PCI_AD (Pin 29) for configuration

transactions to device 13, assert pin PCI_AD (Pin 31)

instead.

R/W

0

28:26

Reserved

Reserved. Masking for devices 12, 11, and 10 is not

implemented. Operation of the PEB383 is unaffected by the

value of these bits.

R

0

25

DEVMSK_9

Device Mask 9

0 = Rerouting disabled for device 9.

1 = Block assertion of PCI_AD (Pin 25) for configuration

transactions to device 9, assert pin PCI_AD (Pin 31)

instead.

R/W

0

24

Reserved

Reserved. Masking for device 8 is not implemented.

Operation of the PEB383 is unaffected by the value of this

bit.

R

0

23

DEVMSK_7

Device Mask 7

0 = Rerouting disabled for device 7.

1 = Block assertion of PCI_AD (Pin 23) for configuration

transactions to device 7, assert pin PCI_AD (Pin 31)

instead.

R/W

0