14. Register Descriptions > Register Map

134

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

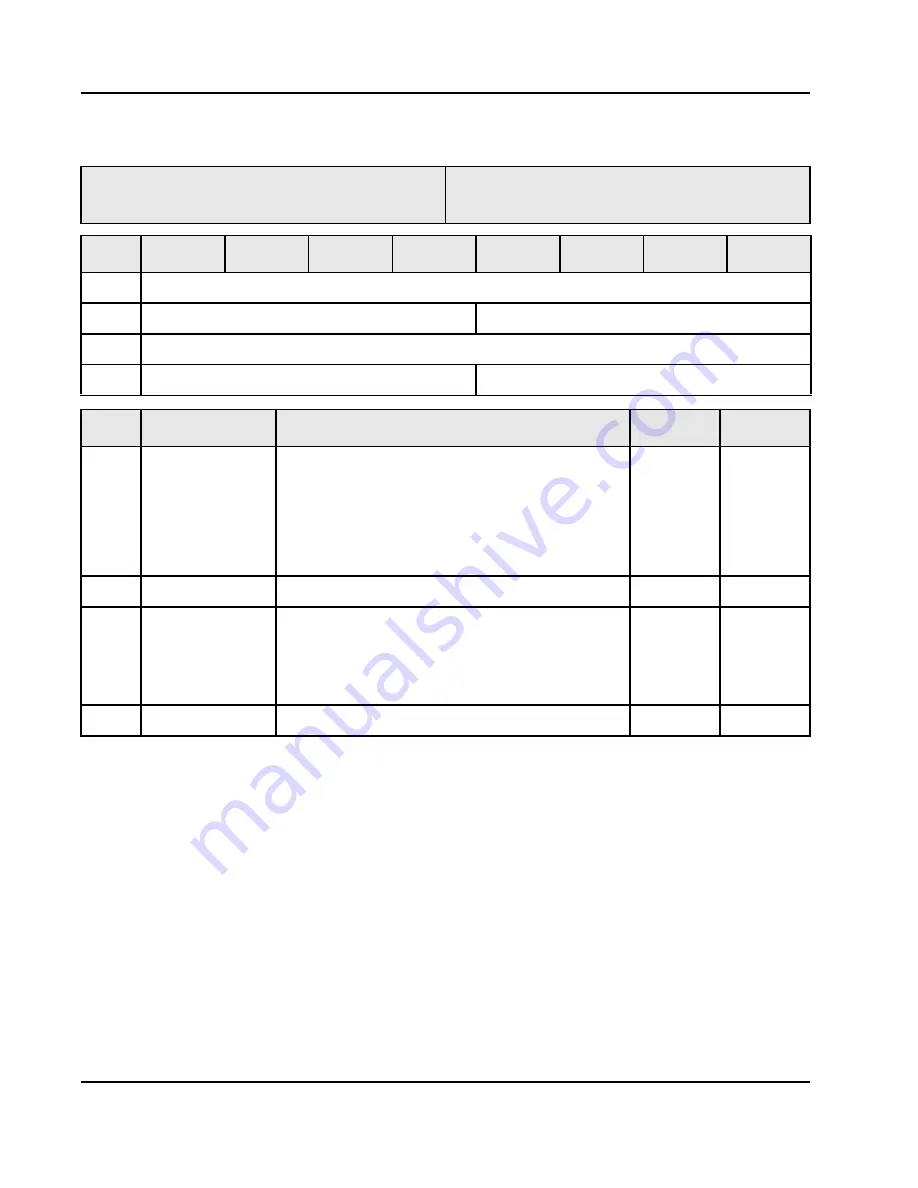

14.3.7

PCI Memory Base and Limit Register

Register name: PCI_MIO_BL

Reset value: 0x0000_0000

Register offset: 0x020

Bits

7

6

5

4

3

2

1

0

31:24

LA

23:16

LA

Reserved

15:08

BA

07:00

BA

Reserved

Bits

Name

Description

Type

Reset value

31:20

LA

Memory Limit Address

This field is used in conjunction with the Memory Base

Address for forwarding memory-mapped I/O transactions.

These bits define the upper bound for the memory address

range. The upper 12 bits correspond to address bits

<31:20> of the address range. Bits <19:0> of the address

range are 0xFFFFF.

R/W

0

19:16

Reserved

Reserved

R

0

15:04

BA

Memory Base Address

This field defines the lower bound of the address range for

forwarding memory-mapped I/O transactions. These bits

correspond to address bits <31:20> of the address range.

The lower 20 address bits (19:0) are 20’h0.

R/W

0

03:00

Reserved

Reserved

R

0