Rev. 1.21

138

�ove��e� ��� 2�1�

Rev. 1.21

13�

�ove��e� ��� 2�1�

HT66F488/HT66F489

A/D Flash MCU with EEPROM

HT66F488/HT66F489

A/D Flash MCU with EEPROM

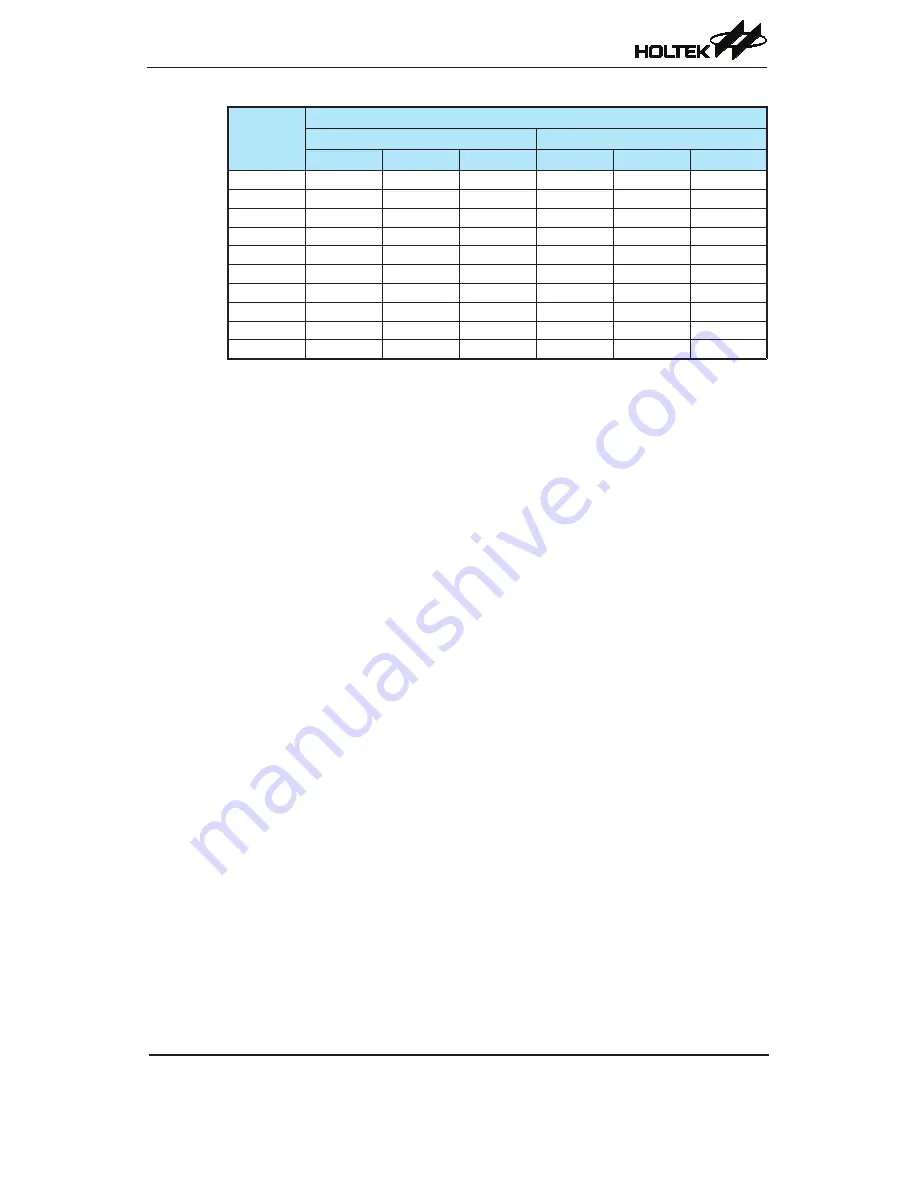

Baud Rate

K/BPS

Baud Rates for BRGH=1

f

SYS

= 16 MHz

f

SYS

= 20 MHz

BRG

Kbaud

Error (%)

BRG

Kbaud

Error (%)

�.3

—

—

—

—

—

—

1.2

—

—

—

—

—

—

2.4

—

—

—

—

—

—

4.8

2��

4.8�8

�.16

—

—

—

�.6

1�3

�.615

�.16

12�

�.615

�.16

1�.2

51

1�.231

�.16

64

1�.231

�.16

38.4

25

38.462

�.16

32

3�.8��

-1.36

5�.6

16

58.824

2.12

21

56.818

-1.35

115.2

8

111.11

-3.55

1�

113.636

-1.36

25�

3

25�

�

4

25�

�

Baud Rates and Error Values for BRGH = 1

UART Setup and Control

For data transfer, the UART function utilizes a non-return-to-zero, more commonly known as NRZ,

format. This is composed of one start bit, eight or nine data bits, and one or two stop bits. Parity

is supported by the UART hardware, and can be setup to be even, odd or no parity. For the most

common data format, 8 data bits along with no parity and one stop bit, denoted as 8, N, 1, is used

as the default setting, which is the setting at power-on. The number of data bits and stop bits, along

with the parity, are setup by programming the corresponding BNO, PRT, PREN, and STOPS bits

in the UCR1 register. The baud rate used to transmit and receive data is setup using the internal

8-bit baud rate generator, while the data is transmitted and received LSB first. Although the UART

transmitter and receiver are functionally independent, they both use the same data format and baud

rate. In all cases stop bits will be used for data transmission.

Enabling/disabling the UART

The basic on/off function of the internal UART function is controlled using the UARTEN bit in the

UCR1 register. If the UARTEN, TXEN and RXEN bits are set, then these two UART pins will act

as normal TX output pin and RX input pin respectively. If no data is being transmitted on the TX

pin, then it will default to a logic high value.

Clearing the UARTEN bit will disable the TX and RX pins and allow these two pins to be used as

normal I/O or other pin-shared functional pins. When the UART function is disabled the buffer will

be reset to an empty condition, at the same time discarding any remaining residual data. Disabling

the UART will also reset the error and status flags with bits TXEN, RXEN, TXBRK, RXIF, OERR,

FERR, PERR and NF being cleared while bits TIDLE, TXIF and RIDLE will be set. The remaining

control bits in the UCR1, UCR2 and BRG registers will remain unaffected. If the UARTEN bit in

the UCR1 register is cleared while the UART is active, then all pending transmissions and receptions

will be immediately suspended and the UART will be reset to a condition as defined above. If the

UART is then subsequently re-enabled, it will restart again in the same configuration.