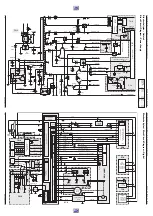

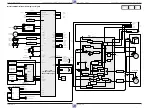

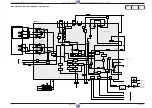

Platinenabbildungen und Schaltpläne / Layout of PCBs and Circuit Diagrams

GV 29…, GV 9000…, GV 9300…

Platinenabbildungen und Schaltpläne / Layout of PCBs and Circuit Diagrams

GV 29…, GV 9000…, GV 9300…

4 - 7

GRUNDIG Service

4 - 8

GRUNDIG Service

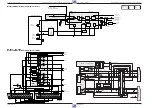

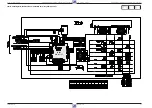

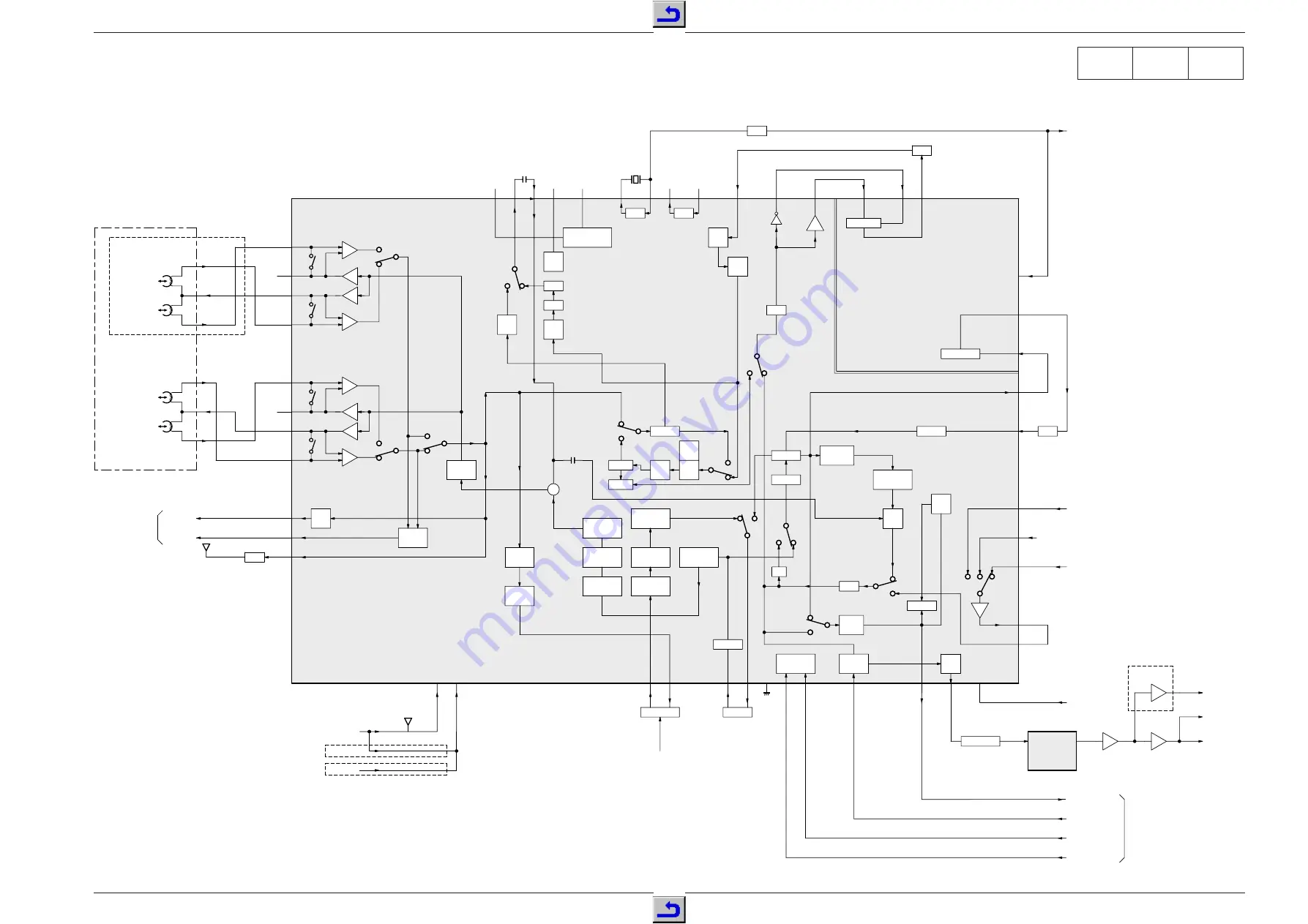

Blockschaltplan / Block Circuit Diagram – Video/Chroma

SP HEAD

TO 3IN1_TUNER

(GV9000/9300)

TO TB-1 IC861

(GV9000/9300)

ROTARY

ONLY GV9300

ONLY GV29/9000

CH1

LP HEAD

CH2

ONLY LP

V OUT

CH1

HEAD DRUM

CH2

HEAD AMP

RF PROCESSING

ENV

DET

COMP

OUT

REC

FM AGC

DET

REC

FM AGC

PB_FM

AGC

+

82

83

85

84

88

89

90

91

93

94

74

ENV DET

ENV SW

BUF

PB ENV

Q1001

KIL

BPF

NAP

KIL

BD

SECAM DET

PAL M DET

73

72

71

70

69

KIL

DET

VXO2

REC

APC

DET

67

66

VXO1

63

64

COMB

AMP

61

59

57

CCD

LPF

C COMB

54

52

51

BUF

Q1005

REC

FM AGC

FM

MOD

W/D

CLIP

FM

DEM

SUB

LPF

DOUBLE

LIM

DETAIL

EMPHA

CLAMP

21

20

1/2

SERIAL

DECODER

22

23

24

Chara

IMS

26

SYNC

SEP

Y-LPF

Y.N.R

NL

DE_EMP

FBC

PIC-CTL

ANR

Y/C

MIX

R

P

PB_Y

PB_C

II PLL

28

6DB

AMP

29

30

PB_EQ

CTL

P

R

ACC

ACC

DET

B-UP

AMP

CONV

BPF2

P

C-LPF

P

R

P

R

BPF1

SYNC

DET

32

31

34

VD IN(TU)

TO TUNER

(GV29)

36

38

VD IN(AV1)

TO CN871 (EURO AV1)

AGC

TC2

CLAMP

DELAYED

SIGNAL

BUF

Q1004

Y_DELAY

41

43

45

46

49

FSC

REC H

BUF

Q1003

EQ AMP

Q1002

Q1013

REC H

18

17

FILTER

Q3061

Q3062

Q3065

VIN

49,50

VOUT

47

Q1012

BUF.

BUF.

Q1001

V OUT

TO CN871 (GV29)

(EURO AV1)

V OUT

TO TUNER (GV29)

ON SCREEN

DISPLAY

C SYNC

V LOCK P

I2C DATA

I2C CLK

RF SWP

11

10

(LA71590M)

PB_PM

EQ.

R

R

P

R

P

4.43MHz

X1002

BUF

Q1006

R

P

R

P

R

P

R

P

CCD

DELAY PROCESSING

TO SY-A

CLK

TO SY-A

TP183

TP182

Q1010

BUF.

IC101

IC301

ONLY GV29

Reference

Oscillograms....4-14

AD-A................4-29

CP-1 ................4-11

MC-A ...............4-19

PW-A ...............4-17

SY-A ................4-18

TB-1.................4-31

TC-A ................4-29

TM-1 ................4-22

TM-A................4-23

VA-A ................4-25