MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

125

CHAPTER 10 WILD REGISTER FUNCTION

10.2 Configuration

10.2

Configuration

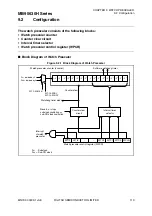

The block diagram of the wild register is shown below. The wild register

consists of the following blocks:

• Memory area block

Wild register data setting register (WRDR0 to WRDR2)

Wild register address setting register (WRAR0 to WRAR2)

Wild register address compare enable register (WREN)

Wild register data test setting register (WROR)

• Control circuit block

■

Block Diagram of Wild Register Function

Figure 10.2-1 Block Diagram of Wild Register Function

Acce

ss

control circ

u

it

Addre

ss

comp

a

re circ

u

it

Decoder

a

nd logic

control circ

u

it

Wild regi

s

ter

a

ddre

ss

comp

a

re en

ab

le regi

s

ter

(WREN)

Wild regi

s

ter d

a

t

a

te

s

t

s

etting regi

s

ter

(WROR)

Wild regi

s

ter d

a

t

a

s

etting

regi

s

ter

(WRDR)

Wild regi

s

ter

a

ddre

ss

s

etting regi

s

ter

(WRAR)

Acce

ss

control circ

u

it

Intern

a

l

bus

Memory

s

p

a

ce

Control circ

u

it

b

lock

Wild regi

s

ter f

u

nction

Memory

a

re

a

b

lock