MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

101

CHAPTER 8 HARDWARE/SOFTWARE WATCHDOG TIMER

8.2 Configuration

8.2

Configuration

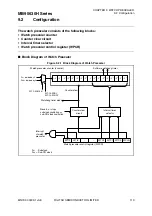

The watchdog timer consists of the following blocks:

• Count clock selector

• Watchdog timer counter

• Reset control circuit

• Watchdog timer clear selector

• Counter clear control circuit

• Watchdog timer control register (WDTC)

■

Block Diagram of Watchdog Timer

Figure 8.2-1 Block Diagram of Watchdog Timer

C

S

0 C

S

P

WTE

3

WTE2

WTE0

WTE1

Co

u

nt clock

s

elector

W

a

tchdog timer

cle

a

r

s

elector

Co

u

nter cle

a

r

control circ

u

it

Re

s

et

control

circ

u

it

Re

s

et

s

ign

a

l

Cle

a

r

s

ign

a

l from

time-

bas

e timer

Cle

a

r

s

ign

a

l from

w

a

tch pre

s

c

a

ler

S

leep mode

s

t

a

rt

s

S

top mode

s

t

a

rt

s

Time-

bas

e timer/w

a

tch mode

s

t

a

rt

s

F

CH

F

CL

2

14

/F

CL

(or 2

1

3

/F

CRL

),

2

1

3

/F

CL

(or 2

12

/F

CRL

)

(W

a

tch pre

s

c

a

ler o

u

tp

u

t)

2

21

/F

CH

(or 2

20

/F

CRH

or 2

20

/F

MCRPLL

),

2

20

/F

CH

(or 2

19

/F

CRH

or 2

19

/F

MCRPLL

)

(Time-

bas

e timer o

u

tp

u

t)

W

a

tchdog

timer co

u

nter

Overflow

W

a

tchdog timer

Activ

a

te

Cle

a

r

W

a

tchdog timer control regi

s

ter (WDTC)

C

S

1

HWWDT

2

16

/F

CRL

(

Sub

-CR timer)

F

CRL

: M

a

in clock

F

CRH

: M

a

in CR clock

F

MCRPLL

: M

a

in CR PLL clock

:

Sub

clock

:

Sub

-CR clock

S

topping or r

u

nning in

s

top mode