Rev.10

79/212

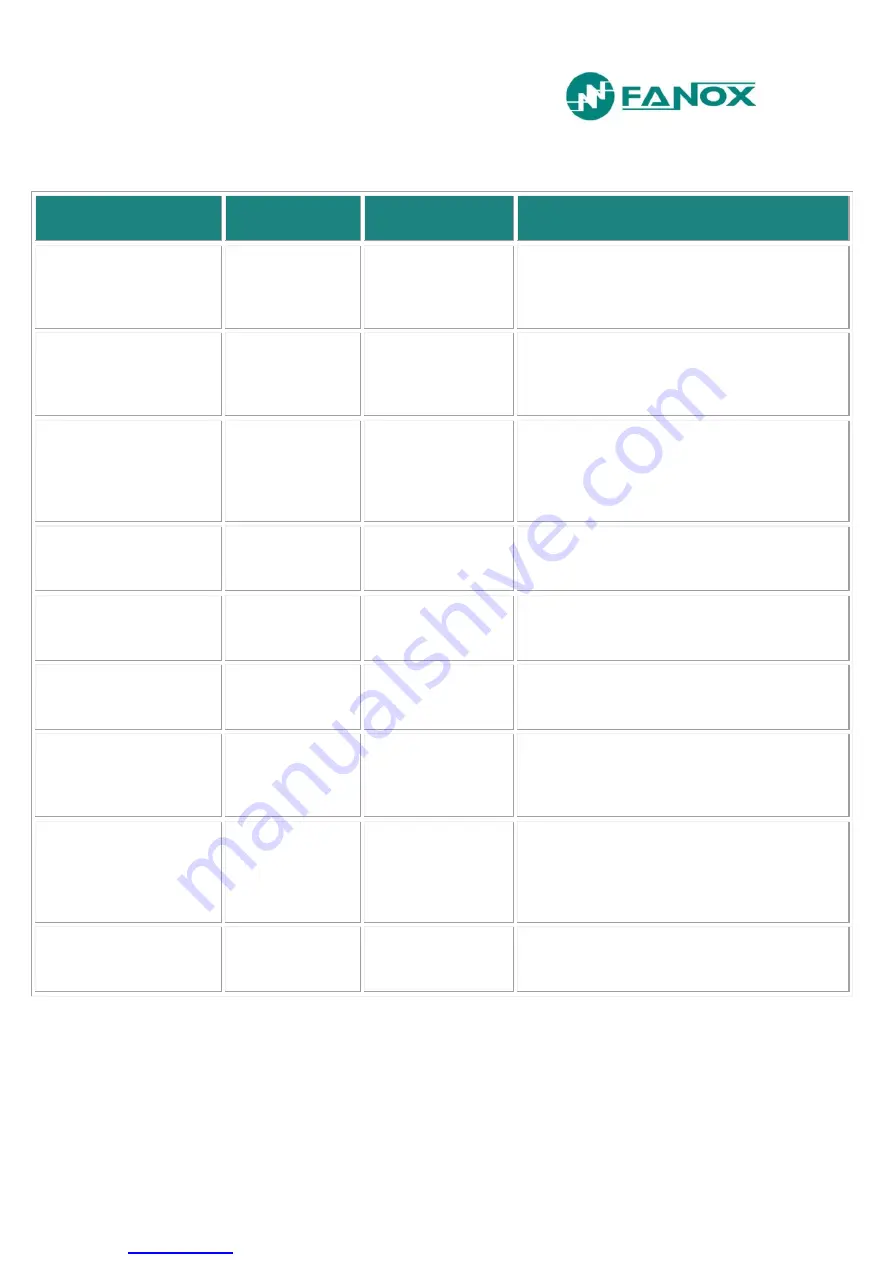

We are going to use a configuration as an example:

OUTPUT

LOGICAL

GATE

BINARY

STATES

DESCRIPTIONS

LED 1

OR4_PULSES

•

Ready

Led On blinks when internal signal “READY” of

general state of the device is activated, this

indicates that the device is working correctly

without any failures.

LED 2

NOR4

•

Ready

Led alarm will activate when internal signal

“READY” of general state of the device is

deactivated, this indicates some failure has

occurred.

LED 3

OR4_LACTH

•

General Trip

Led trip will activate when internal signal

“GENERAL TRIP” of general state of the device is

activated, this indicates that some protection

function has tripped. This led will continue

activated until the reset of the leds is made.

Output 1

OR4

•

Local opening

•

General trip

Trip output will activate when there is a general

trip or when 52 opening command is carried out,

from local communications or from HMI.

Output 2

OR4

•

Local closing

Output 2 will be activated when 52 closing

command is carried out from local communications

or from HMI.

52b

OR4

•

Input-2

When physical input 2 is activated, 52a logical

output will be activated, and it will used to

determine the breaker state.

External trip

OR4

•

Input-1

When physical input 1 is activated external trip

logical output will be activated, and it will be used

to generate a general trip by general protection

function.

BF Init

OR4

•

Local opening

•

Remote opening

•

General trip

When a general trip has occurred or when 52a

opening command is carried out from local

communications start BF logical output will be

activated and it will be used to initiate the

detection of breaker failure by BF function.

Fault Init

OR4_LACTH

•

General trip

When general trip is activated, fault start logical

output will be activated and it will generate a new

fault register.

5.10. 86 Function. Trip Output Lockout

When the trip output is configured like OR_LACTH the programmable logic allows this

output to block.

Summary of Contents for SIL-V

Page 7: ...www fanox com Rev 10 7 212 2 DIMENSIONS AND CONNECTION DIAGRAMS 2 1 Equipment front view...

Page 8: ...www fanox com Rev 10 8 212 2 2 Equipment dimensions...

Page 9: ...www fanox com Rev 10 9 212 2 3 Cut out pattern...

Page 11: ...www fanox com Rev 10 11 212 3 VT configuration phase neutral...

Page 12: ...www fanox com Rev 10 12 212 3 VT configuration phase neutral residual voltage SILVxxxx0xxxxx...

Page 13: ...www fanox com Rev 10 13 212 3 VT configuration phase neutral busbar voltage SILVxxxx2xxxxx...

Page 14: ...www fanox com Rev 10 14 212 3VT configuration phase phase residual voltage...

Page 15: ...www fanox com Rev 10 15 212 2VT configuration phase phase residual voltage...

Page 17: ...www fanox com Rev 10 17 212 2 5 Terminals...

Page 25: ...www fanox com Rev 10 25 212 3 3 Functional Diagram...

Page 192: ...www fanox com Rev 10 192 212...

Page 211: ...www fanox com Rev 10 211 212 NOTES...

Page 212: ...www fanox com Rev 10 212 212...