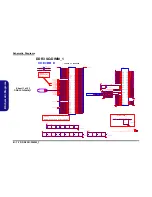

Schematic Diagrams

CPU 2/7 (CLK, MISC, JTAG) B - 5

B.Sch

e

m

a

tic D

iag

rams

CPU 2/7 (CLK, MISC, JTAG)

+1.5S_CPU 7,37

1.1VS_VTT_PW RGD

21,41

Q13

* MTN7002Z H S3

G

D

S

R 162

*10K_04

3.3V

3.3V

+1.5S_C PU

U 11

*74AH C 1G08GW

1

2

5

4

3

DR AMPWR GD_CPU

Q12

*2N3904

B

E

C

+1.5S_CPU_PWR GD 40

3.3V

C 222

*.1u_10V_X7R _04

R 163

* 10K_04

SY S_AGENT_PW ROK

H _C PU R ST#

DDR3 Compensation Signals

H_PR OC H OT#_D

Processor Pullups

XD P_TD I_M

XD P_TR ST#

1. 5V

10,11,31,37, 40

H _PROC HOT#

43

If PROCHOT# is not used, then it must be terminated

with a 50-O pull-up resistor to VTT_1.1 rail.

PROCESSOR 2/7 ( CLK,MISC,JTAG )

H _C OMP2

H _C OMP3

H _C OMP1

H _C OMP0

R107

*68_04

R128

* 12.4K_1%_04

R67

*51_04

R69

*51_04

R130

10K_04

R 159

1. 5K_1%_04

R125

49.9_1%_04

R421

20_1%_04

R 110

0_04

R153

* 0_04

R440

24.9_1%_04

R419

49.9_1%_04

R418

51_04

R60

*51_04

R131

10K_04

C

L

OC

KS

MIS

C

T

HE

R

MA

L

P

WR

MA

N

AG

EME

N

T

D

DR3

MI

S

C

J

T

AG

&

B

PM

U 40B

PZ98927-3641-01F

SM_RC OMP[1]

AM1

SM_RC OMP[2]

AN1

SM_D RAMRST#

F6

SM_RC OMP[0]

AL1

BCLK#

B16

BC LK

A16

BC LK_ITP#

AT30

BC LK_I TP

AR30

PEG_CLK#

D 16

PEG_C LK

E16

DPLL_R EF_SSCLK#

A17

D PLL_REF_SSC LK

A18

C ATERR#

AK14

C OMP3

AT23

PEC I

AT15

PR OCH OT#

AN 26

THERMTR IP#

AK15

R ESET_OBS#

AP26

VC C PW R GOOD_1

AN 14

VC C PW R GOOD_0

AN 27

SM_DR AMPWR OK

AK13

VTTPWRGOOD

AM15

R STIN #

AL14

PM_EXT_TS#[0]

AN15

PM_EXT_TS#[1]

AP15

PR D Y#

AT28

PR EQ#

AP27

TCK

AN28

TMS

AP28

TRST#

AT27

TDI

AT29

TD O

AR27

TDI _M

AR29

TD O_M

AP29

D BR#

AN25

BPM#[0]

AJ 22

BPM#[1]

AK22

BPM#[2]

AK24

BPM#[3]

AJ 24

BPM#[4]

AJ 25

BPM#[5]

AH22

BPM#[6]

AK23

BPM#[7]

AH23

C OMP2

AT24

PM_SY NC

AL15

TAPPW R GOOD

AM26

C OMP1

G16

C OMP0

AT26

SKTOCC#

AH 24

R109

68_04

R424

20_1%_04

R 115

*0_04

R129

* 0_04

TRACE WIDTH 10MIL, LENGTH <500MILS

R441

100_1%_04

R 155

750_1%_04

R433

49.9_1%_04

R108

51_04

R68

*51_04

R439

130_1%_04

XD P_TMS

1.1VS_VTT

1.1VS_VTT

1.1VS_VTT

BCLK_CPU _P 24

CLK_D P_P 20

CLK_D P_N 20

H_CPU PWR GD

24

BUF_PLT_R ST#

23,28,31, 32,36

PM_D RAM_PWRGD

21

H _VTTPWR GD

21

BCLK_CPU _N 24

H _TH RMTRIP#

24

CLK_EXP_N 20

CLK_EXP_P 20

1. 1VS_VTT 2, 6,7,19,20,21, 24,25,26,39, 41, 42,43

H _PEC I

24,36

PM_EXTTS#_EC 3

TS#_DIMM0_1 10,11

DELAY _PW R GD

21, 43

H_PM_SYN C

21

R 134

1.1K_1%_04

VD D PW R GOOD_R

R 158

3K_1%_04

+1. 5S_C PU

R157

*1.5K_1%_04

D RAMPWR GD_CPU

R 114

*10m il_short

H _PROC HOT#_D

R 156

*10m il_short

C 1126

0.1u_10V_X7R _04

R 416

*10m il_short

XDP_TDO_M

H_CPUR ST#

Processor Compensation

Signals

H_PW R GD _XD P

PLT_R ST#_R

XDP_PR EQ#

XDP_TCLK

XDP_TRST#

XDP_TMS

Connect to the Processor (VTTPWRGOOD) VTT_1.1 VR power

good signal to processor. Signal voltage level is 1.1 V.

H_COMP3

SY S_AGENT_PWR OK

H_COMP2

PM_EXTTS#[1]

H_COMP1

Signal from PCH to Processor

Connect to PCH (PLT_RST#)

(needs to be level translated

from 3.3 V to 1.1 V).

C PU _DR AMR ST#

SM_R COMP_0

XD P_TD O_M

3. 3V

3,12, 13,17,19,20, 21, 23,24,26,28, 29,31,32,33,34, 37,39,40,41,44

XD P_TD I_R

SM_R COMP_1

VD DPW RGOOD _R

SM_R COMP_2

H_CATERR#

XD P_PREQ#

XD P_TC LK

R 246

*1K_04

Q32

* MTN 7002Z H S3

G

D

S

R 241

*100K_04

R 250

0_04

XDP_TDI _R

R 234

* 0_04

D DR 3_DR AMR ST#

10,11

1.5V

D DR 3_DR AMRST#

DR AMR ST_C N TR L_PC H

24

C PU _DR AMR ST#

C360

* 470p_50V_X7R_04

PM_EXTTS#[0]

DR AMR ST_C N TR L

9

H_COMP0

XDP_TDI _M

XD P_TDO_M

R 121

0_04

SM_R COMP_2

SM_R COMP_1

SM_R COMP_0

H _C ATER R #

Sheet 4 of 53

CPU 2/7

(CLK, MISC, JTAG)

Summary of Contents for B7110 Service

Page 1: ......

Page 2: ......

Page 3: ...Preface I Preface Notebook Computer B7110 Service Manual ...

Page 24: ...Introduction 1 12 1 Introduction ...

Page 43: ...Part Lists Top A 3 A Part Lists Top Figure A 1 Top 黑色 非耐落 灰色 ...

Page 44: ...Part Lists A 4 Bottom A Part Lists Bottom Figure A 2 Bottom ...

Page 45: ...Part Lists LCD A 5 A Part Lists LCD Figure A 3 LCD 非耐落 ...

Page 46: ...Part Lists A 6 HDD A Part Lists HDD Figure A 4 HDD ...