72

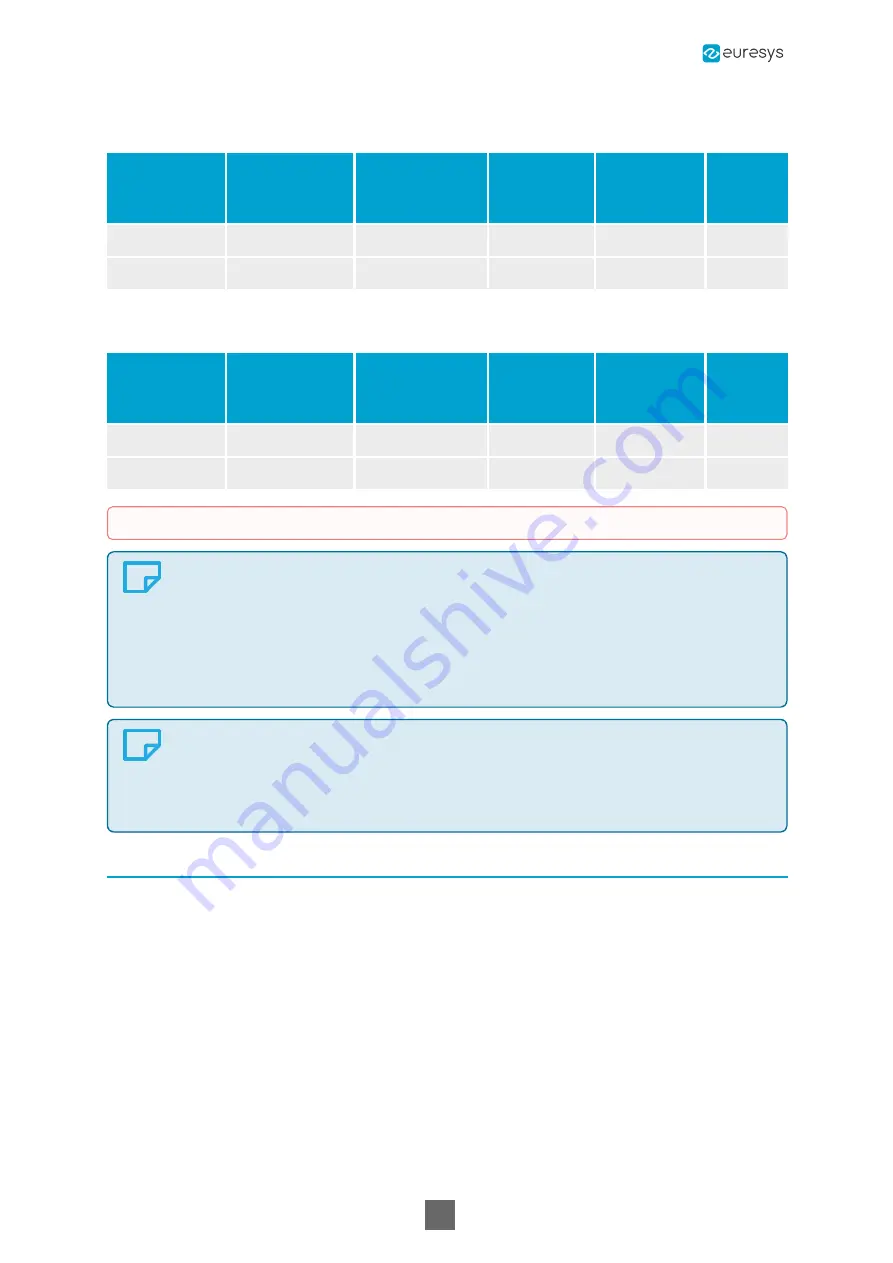

Voltage levels and margins in a TTL (5 V) system, R = 180

ohm

Isolated

Output

Logic Level

Isolated Output

State

Isolated Output

Voltage Level

TTL Input

Voltage

Level

Voltage

Margin

TTL Input

Logic

Level

High

Close

4.1 V max

(2)

2.0 V min

2.1 V

High

Low

Open

0.36 V max

(1)

0.8 V max

0.44 V

Low

Voltage levels and margins in a LVTTL (3.3 V) system, R = 180 ohm

Isolated

Output

Logic Level

Isolated Output

State

Isolated Output

Voltage Level

TTL Input

Voltage

Level

Voltage

Margin

TTL Input

Logic

Level

High

Close

2.4 V min

(2)

2.0 V min

0.4 V

High

Low

Open

0.36 V max

(1)

0.8 V max

0.44 V

Low

See also:

for voltage levels of isolated outputs.

NOTE

(1) 0.36 V is obtained considering a worst-case external (pull-up) load of 2

mA ( 180 ohm x 2 mA = 0.36 V), which means that the circuit can support the

presence of an external pull-up resistor up to a (minimum) value of 1K5 ohm

(in 3.3 V) or 2K4 ohm (in 5 V). If needed, an other R value can be chosen

according to the actual pull-up load within the circuit.

NOTE

(2) In any case, the voltage drop across the opto-coupler pins (V

OUT

+

- V

OUT

t

-

) is lower than 0.9 V. Which gives the following results: 3.3 V – 0.9 V = 2.4 V; 5

V – 0.9 V = 4.1 V.

Dynamic limitations

The maximum pulse width of isolated outputs is about 5 µs and the maximum pulse rate is 100

KHz,

Isolated outputs add an extra delay of about 5 µs in the signal propagation.

The resistor value of R = 180 ohm has good dynamic results for a usual capacitive loads as 1 or

2 meters of cable. As example, a 2m cable will add 100 pF of load (50pF/m) which give a rise

time of about 18 µs at 180 ohm ( R x C = 180 ohm x 100 pF = 18 µs ) . If needed, the R value can

be adapted to match special requirements in terms of rise time and/or capacitive load.

Coaxlink

Hardware Manual

Summary of Contents for Coaxlink 1629

Page 4: ...4 1 About This Document 1 1 Document Scope 5 Coaxlink Hardware Manual ...

Page 7: ...7 2 1 Board and Bracket Layouts Coaxlink Hardware Manual ...

Page 9: ...9 2 2 Connectors Coaxlink Hardware Manual ...

Page 17: ...17 2 3 LEDs Coaxlink Hardware Manual ...

Page 33: ...33 3 3 Power Distribution Schemes Coaxlink Hardware Manual ...

Page 64: ...64 6 Appendix Appendix to Coaxlink cards hardware manual Coaxlink Hardware Manual ...