Prometheus CPU User Manual V1.44

Page 20

6.4 Watchdog Timer

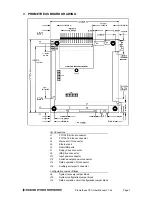

Prometheus contains a watchdog timer circuit consisting of two programmable timers, WD1 and

WD2, cascaded together. The input to the circuit is WDI, and the output is WDO. Both signals

appear on I/O connector WDI may be triggered in hardware or in software. A special “early”

version of WDO may be output on the WDO pin. When this signal is connected to WDI, the

watchdog circuit will be retriggered automatically. A block diagram is provided here:

The duration of each timer is user-programmable. When WD1 is triggered, it begins to count

down. When it reaches zero, it triggers WD2 and may also generate a user-selectable

combination of these events:

♦

Non-maskable interrupt (NMI)

♦

System controller interrupt (SCI)

♦

System Management interrupt (SMI)

♦

Hardware

reset

WD2 then begins to count down. When WD2 counter reaches zero, it will unconditionally cause a

hardware reset. The WD2 timer is provided to give external circuits time to respond to the WDO

event before the hardware reset occurs.

The watchdog timer circuit is programmed via I/O registers 0CH through 12H. Detailed

programming information is in the ZFx86 Training Manual included in the Documents folder of the

Prometheus CD. The watchdog timer is supported in the DSC Universal Driver software version

5.1 and later.