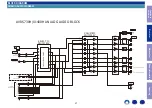

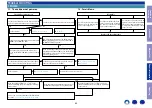

PCM9211PTR BLOCK DIAGRAM

Clock/ Data

Recovery

MPIO_ A

SELECTOR

MPIO_ C

SELECTOR

MPIO _B

SELECTOR

ADC

Com. Supply

MPO0/1

SELECTOR

MPO 0

MPO 1

MAIN

OUTPUT

SCKO

BCK

LRCK

DOUT

PORT

RXIN8

RXIN9

RXIN10

RXIN11

DITOUT

AUTO

DIR

ADC

AUXIN0

AUXIN1

AUXIN2

AUTO

DIR

ADC

AUXIN0

AUXIN1

AUXIN2

AUTO

DIR

ADC

AUXIN0

AUXIN1

DIT

Lock :DIR

Unlock:ADC

AUXIN 2

AUXOUT

OSC

Divider

XMCKO

Divider

XMCKO

DITOUT

RECOUT 0

RECOUT 1

AUXIN 0

AUXIN1

ADC Standalone

ADC Mode

Control

Function

Control

REGISTER

POWER SUPPLY

MC /SCL

MDI /SDA

MDO /ADR 0

MS/ADR 1

FILT

PLL

DIR

Lock Detection

ERROR /INT0

NPCM /INT1

ADC Clock

(SCK /BCK/LRCK)

(To MPIO _A & MPO0/1 )

ADC

MODE

DIR CS

( 48-bit)

DIT CS

( 48-bit)

DIR Interrupt

GPIO/GPO

Data

MPIO_ A

MPIO_ B

MPIO_ C

MPO0

MPO1

Divider

( to MPIO_A )

Secondary BCK / LRCK

Selector

RECOUT0

RECOUT1

SBCK /SLRCK

DOUT

RXIN7

SCKO/ BCK/LRCK

RXIN 0

RXIN 1

RXIN 2

RXIN 4/ASCKI 0

RXIN 3

RXIN 5/ABCKI 0

RXIN 6/ALRCKI 0

RXIN 7/ADIN0

RXIN7

RXIN6

RXIN5

RXIN4

RXIN3

RXIN2

RXIN1

RXIN0

MPIO_ A0

MPIO_ A1

MPIO_ A2

MPIO_ A3

VINL

VINR

VCOM

MPIO _C0

MPIO _C1

MPIO _C2

MPIO _C3

XTI

XTO

AGND

VDDRX

GNDRX

DVDD

VCCAD

AGNDAD

DGND

VCC

ADC

ANALOG

DIR

ANALOG

ALL

DIR

ANALOG

SPI/I C

INTERFACE

2

Reset

and Mode

Set

All Port

f Calculator

S

DIR

f Calculator

S

DIR

P and P

C

D

EXTRA DIR FUNCTIONS

f Calculator

S

ERROR DETECTION

Non-PCM DETECTION

Flags

DTS-CD/LD Detection

Validity Flag

User Data

Channel Status Data

BFRAME Detection

Interrupt System

MPIO_B3

MPIO_B2

MPIO_B1

MPIO_B0

RST

PCM9211

www.ti.com

SBAS495 –JUNE 2010

BLOCK DIAGRAM

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

9

Product Folder Link(s):

PCM9211

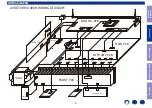

CS49844A-CQZ (DIGITAL_DSP : IC781)

VDD3

BDI*, DAI1_SCLK1, GPIO71

BDI*, DAI1_D0, GPIO64

GNDIO4

VDDIO4

SD_D2, EXT_D10

SD_D11, EXT_D3

SD_D15, EXT_D7

SD_D12, EXT_D4

DAO3_D3, XMTA, GPIO113

SD_D14, EXT_D6

SD_D7, EXT_D15

SD_D13, EXT_D5

GND10

SD_D0, EXT_D8

SD_D3, EXT_D11

SD_D5, EXT_D13

SD_D1, EXT_D9

VDD9

DAO3_D7, XMTB, GPIO115

DAO3_D2, GPIO33

SCP_MOSI, GPIO147

SCP1_MISO_SDA, GPIO146

SCP1_CLK, GPIO148

SCP2_CS

SCP1_IRQ, GPIO144_OD

DAI1_SCLK2, GPIO73

VDDIO1

GNDIO1

DAI1_LRCK2, GPIO72

RESET

DBDA1

DBCK0

EE_CS0, GPIO1

DAI1_D4, GPIO68

BDI*, DAI1_D2, GPIO66

BDI*, DAI1_D1, GPIO65

SD_CS, EXT_OE

SD_BA0, EXT_A13

SD_CAS, EXT_CS2

GND1

VDD2

DAI1_D5, GPIO69

EE_CS1. GPIO0

VDD10

BDI* DAI1_D3, GPIO67

VDD1

GND2

TEST_EN

SD_BA1, EXT_A14

GND3

BDI*, DAI1_LRCK1, GPIO70

SD_A10, EXT_A12

DBDA0

DBCK1

GND8

VDD8

SCP1_CS, GPIO145

SD_D4, EXT_D12

GND9

SCP_BSY, GPIO143_OD

DA03_D1, GPIO32

DA03_D5, GPIO34

DAO3_D6, GPIO35

SD_DQM0, EXT_A15

SD_WE, EXT_WE

SD_A3, EXT_A3,

SD_A2, EXT_A2

SD_D6, EXT_D14

SD_RAS, EXT_CS1

SD_A1, EXT_A1

SD_A0, EXT_A0

1

5

9

10

13

18

21

24

27

33

36

15

25

30

35

101

98

94

91

86

83

76

73

75

80

85

90

95

100

105

108

CS49844A

144-Pin LQFP

Package

(with Thermal Pad)

50

Caution in

servicing

Electrical

Mechanical

Repair Information

Updating

Summary of Contents for AVR-S730H

Page 148: ...www denon com ...