MSC SM2S-IMX8M User Manual

39 / 92

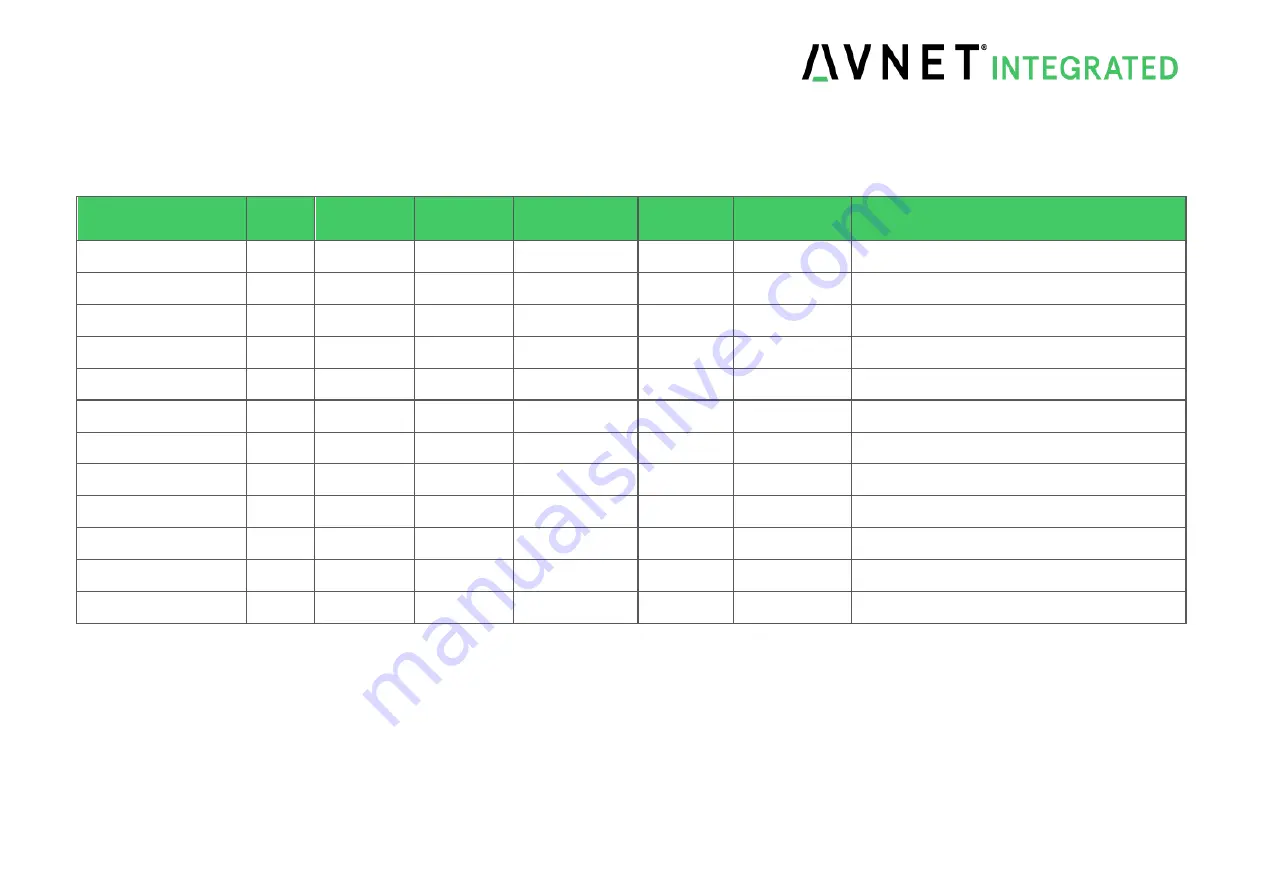

4.10 GPIO

The CPU GPIO can be used with default Linux GPIO SYSFS interface in user space.

Table 4-10: GPIO Signal Description

Signal

Pin

Type

Signal

Level

Pin on

i.MX8M

Pin name on

i.MX8M

Power

Tolerance

PU/PD

Description

GPIO0 / CAM0_PWR# I/O

1.8V CMOS

T6

GPIO1_IO00

1.8V

PU 470K 1.8V

CPU GPIO1_IO00

GPIO1 / CAM1_PWR# I/O

1.8V CMOS

K22

NAND_RE_B

1.8V

PU 470K 1.8V

CPU GPIO3_IO17

GPIO2 / CAM0_RST#

I/O

1.8V CMOS

P4

GPIO1_IO03

1.8V

PU 470K 1.8V

CPU GPIO1_IO03

GPIO3 / CAM1_RST#

I/O

1.8V CMOS

G21

NAND_CE1_B

1.8V

PU 470K 1.8V

CPU GPIO3_IO02

GPIO4 / HDA_RST#

I/O

1.8V CMOS

P7

GPIO1_IO05

1.8V

PU 470K 1.8V

CPU GPIO1_IO05

GPIO5 / PWM_OUT

I/O

1.8V CMOS

T7

GPIO1_IO01

1.8V

PU 470K 1.8V

CPU GPIO1_IO01 / PWM1_OUT

GPIO6 / TACHIN

I/O

1.8V CMOS

N5

GPIO1_IO06

1.8V

PU 470K 1.8V

CPU GPIO1_IO06

GPIO7

I/O

1.8V CMOS

N6

GPIO1_IO07

1.8V

PU 470K 1.8V

CPU GPIO1_IO07

GPIO8

I/O

1.8V CMOS

N7

GPIO1_IO08

1.8V

PU 470K 1.8V

CPU GPIO1_IO08

GPIO9

I/O

1.8V CMOS

M6

GPIO1_IO09

1.8V

PU 470K 1.8V

CPU GPIO1_IO09

GPIO10

I/O

1.8V CMOS

F21

NAND_CE2_B

1.8V

PU 470K 1.8V

CPU GPIO3_IO03

GPIO11

I/O

1.8V CMOS

L6

GPIO1_IO011

1.8V

PU 470K 1.8V

CPU GPIO1_IO11