101

AT94KAL Series FPSLIC

Rev. 1138G–FPSLI–11/03

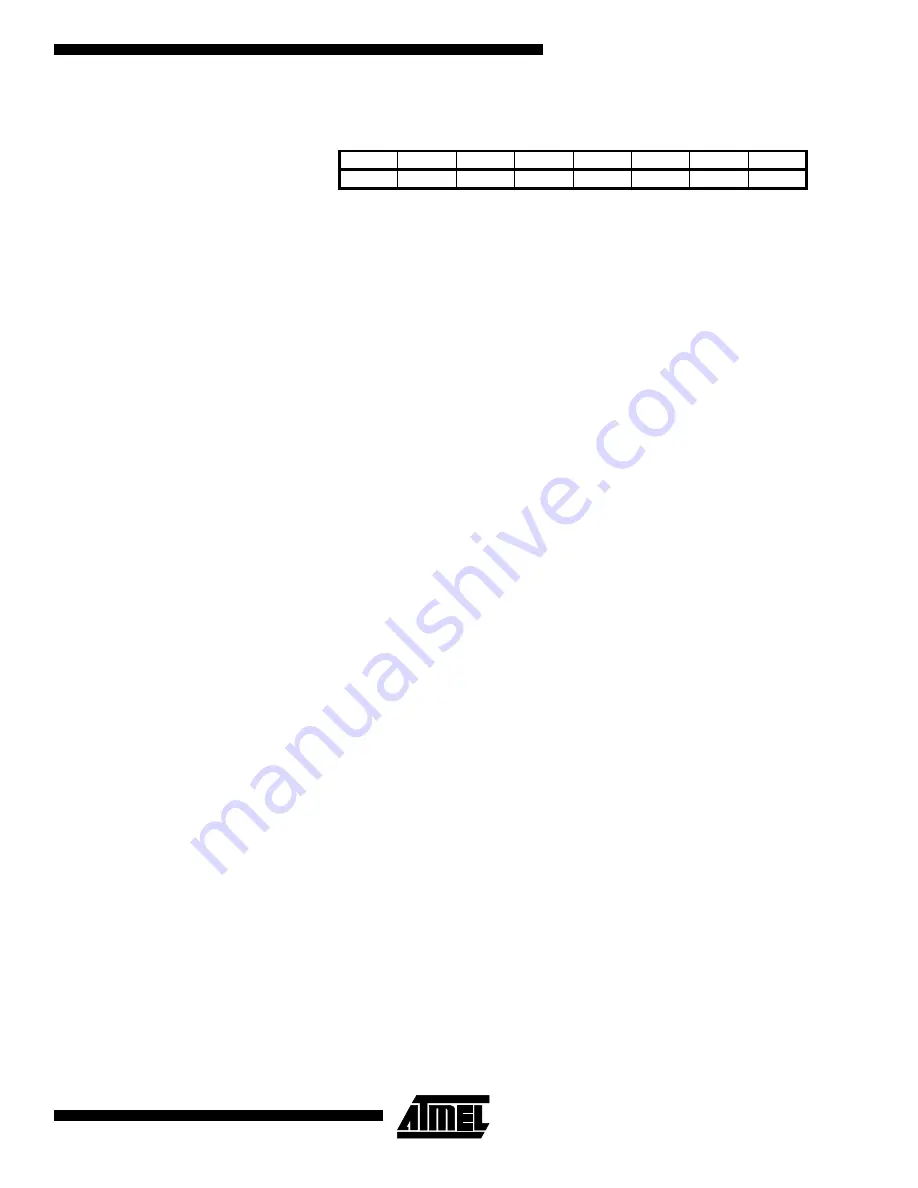

Timer/Counter1 Input Capture Register – ICR1H AND ICR1L

The input capture register is a 16-bit read-only register.

When the rising or falling edge (according to the input capture edge setting – ICES1) of the

signal a t the input capture pin – PE7(ICP) – is detected , the current value of the

Timer/Counter1 Register – TCNT1 is transferred to the Input Capture Register – ICR1. In the

same cycle, the input capture flag – ICF1 – is set (one).

Since the Input Capture Register – ICR1 – is a 16-bit register, a temporary register TEMP is

used when ICR1 is read to ensure that both bytes are read simultaneously. When the CPU

reads the low byte ICR1L, the data is sent to the CPU and the data of the high byte ICR1H is

placed in the TEMP register. When the CPU reads the data in the high byte ICR1H, the CPU

receives the data in the TEMP register. Consequently, the low byte ICR1L must be accessed

first for a full 16-bit register read operation.

The TEMP register is also used when accessing TCNT1, OCR1A and OCR1B. If the main pro-

gram and also interrupt routines perform access to registers using TEMP, interrupts must be

disabled during access from the main program and interrupt routine.

Timer/Counter1 in

PWM Mode

When the PWM mode is selected, Timer/Counter1 and the Output Compare Register1A –

OCR1A and the Output Compare Register1B – OCR1B, form a dual 8-, 9- or 10-bit, free-run-

ning, glitch-free and phase correct PWM with outputs on the PD6(OC1A) and PE5(OC1B)

pins. In this mode the Timer/Counter1 acts as an up/down counter, counting up from $0000 to

TOP (see Table 30), where it turns and counts down again to zero before the cycle is

repeated. When the counter value matches the contents of the 8, 9 or 10 least significant bits

(depends of the resolution) of OCR1A or OCR1B, the PD6(OC1A)/PE5(OC1B) pins are set or

cleared according to the settings of the COM1A1/COM1A0 or COM1B1/COM1B0 bits in the

Timer/Counter1 Control Register TCCR1A. Refer to Table 31 for details.

Alternatively, the Timer/Counter1 can be configured to a PWM that operates at twice the

speed as in the mode described above. Then the Timer/Counter1 and the Output Compare

Register1A – OCR1A and the Output Compare Register1B – OCR1B, form a dual 8-, 9- or 10-

bit, free-running and glitch-free PWM with outputs on the PE6(OC1A) and PE5(OC1B) pins.

As shown in Table 30, the PWM operates at either 8-, 9- or 10-bit resolution. Note the unused

bits in OCR1A, OCR1B and TCNT1 will automatically be written to zero by the hardware. For

example, bit 9 to 15 will be set to zero in OCR1A, OCR1B and TCNT1 if the 9-bit PWM resolu-

tion is selected. This makes it possible for the user to perform read-modify-write operations in

any of the three resolution modes and the unused bits will be treated as “don’t care”.

Bit

15

14

13

12

11

10

9

8

$25 ($45)

MSB

ICR1H

$24 ($44)

LSB

ICR1L

7

6

5

4

3

2

1

0

Read/Write

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0