[AK4493]

017012230-E-00

2017/12

- 16 -

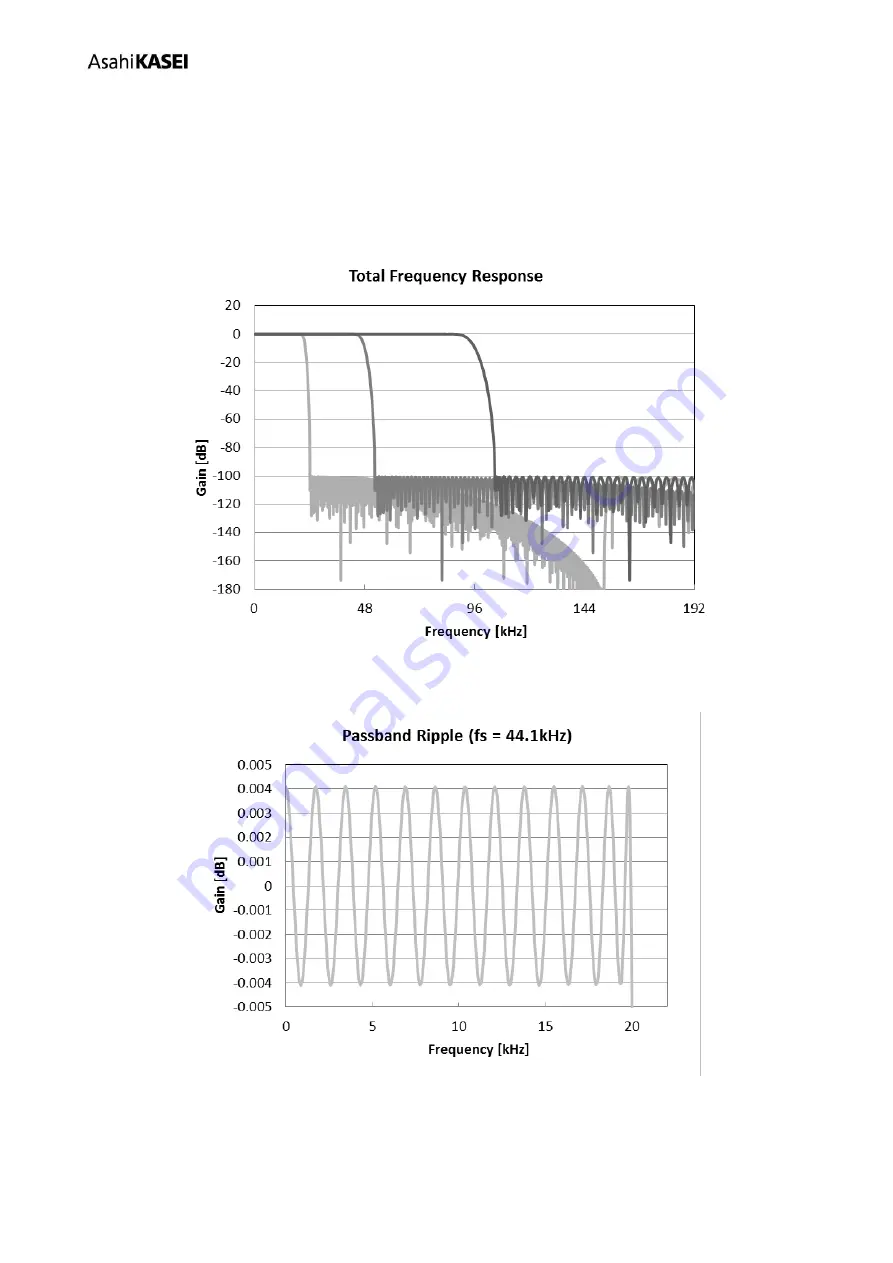

Note 27. The passband and stopband frequencies scale with fs. For example, PB = 0.4535×fs

(@

0.01dB), SB = 0.546×fs.

Note 28. This value is the gain amplitude of first step interpolator which is 4 times oversampling filter in

pass band width.

Note 29. The calculating delay time which occurred by digital filtering. This time is from setting the

16/20/24/32 bit data of both channels to the output of analog signal.

Figure 3. Sharp Roll-off Filter Frequency Response

Figure 4. Sharp Roll-off Filter Passband Ripple