IPMI Feature Set

ATCA-7480 Installation and Use (6806800T17A)

309

EEPROMU

- Verifies that the EEPROM contents are readable via I2C. Since the IPMC stores

its runtime and persistent data here, proper operation is crucial.

Master-Only I2CU

- Verifies that all expected devices attached to the master-only I2C bus

are accessible.

To obtain results of POST, the IPMC supports the IPMI standard command,

Get Self Test

Results

with OEM extensions. This IPMI command can be run at anytime.

9.5

Ejector Handle De-Bounce

The handle switch de-bouncing algorithm is used to configure a programmable delay. The

IPMC waits before ejector handle state changes are accepted. This is provided to avoid

accidental FRU extraction caused by service-teams during servicing other FRUs.

The ejector handle de-bounce function can be enabled, disabled and configured with the use

of the OEM command,

Set/Get Feature Configuration

. For details, see

9.6

FRU Inventory

The ATCA-7480 implements two intelligent FRUs (IPMC and MMC).

Every FRU provides its own FRU information (serial, part, MAC addresses). Depending on the

presence of a module, its FRU information is visible or not.

The FRU of the RTM is not hot-swappable. This is especially important to ensure that the system

management application (HPI-B) does not has to deal with dynamic FRU population.

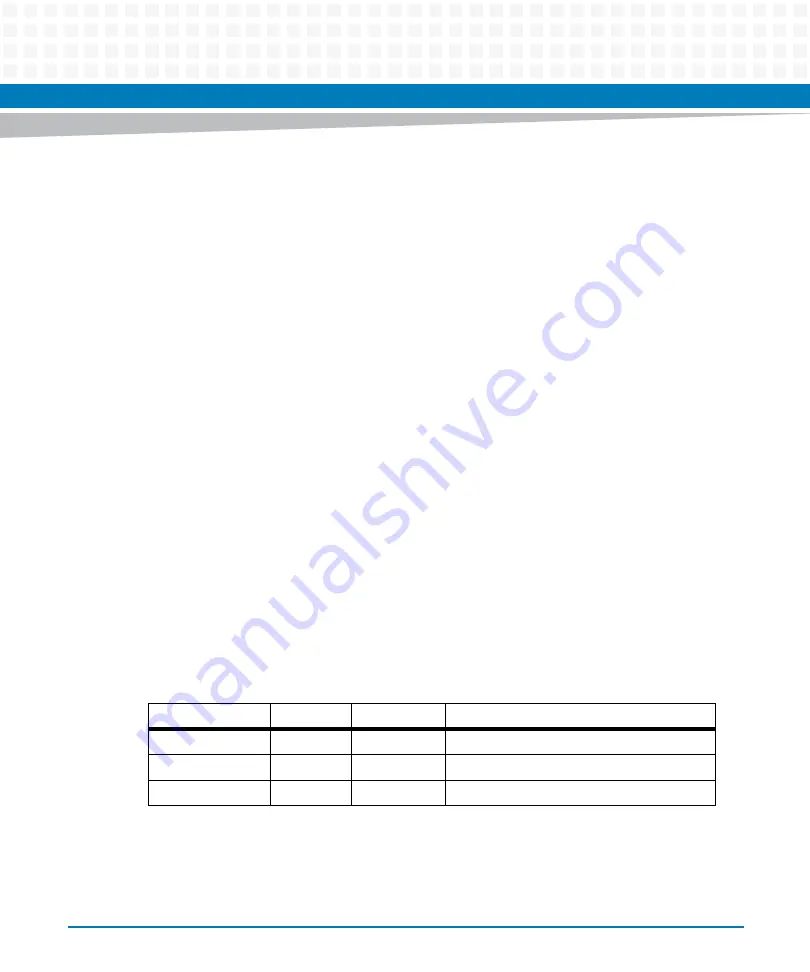

Table 9-6 FRU information and SEL at EEPROM storage

I2C Address

I2C bus

Domain

Purpose

0xA0

IPMC

Front blade

SEL

0xA2

IPMC

Front blade

FRU Information and Bios Boot Parameter

Device internal

MMC

RTM

FRU Information

Summary of Contents for ATCA-7480

Page 1: ...ATCA 7480 Installation and Use P N 6806800T17A February 2015...

Page 24: ...ATCA 7480 Installation and Use 6806800T17A About this Manual 24 About this Manual...

Page 30: ...ATCA 7480 Installation and Use 6806800T17A Safety Notes 30...

Page 36: ...ATCA 7480 Installation and Use 6806800T17A Sicherheitshinweise 36...

Page 42: ...Introduction ATCA 7480 Installation and Use 6806800T17A 42...

Page 64: ...Hardware Preparation and Installation ATCA 7480 Installation and Use 6806800T17A 64...

Page 82: ...Controls Indicators and Connectors ATCA 7480 Installation and Use 6806800T17A 82...

Page 98: ...Functional Description ATCA 7480 Installation and Use 6806800T17A 98...

Page 222: ...BIOS ATCA 7480 Installation and Use 6806800T17A 222...

Page 326: ...Replacing the Battery ATCA 7480 Installation and Use 6806800T17A 326...

Page 329: ......