ADSP-2126x SHARC Processor Hardware Reference

A-111

Registers Reference

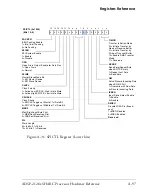

Parallel Port DMA Transmit Register (TXPP)

This register’s address is 0x1808. This Transmit Data register is a 32-bit

register that is part of the IOP register set and can be accessed by the core

or the DMA controller. Data is loaded into this register before being

transmitted. Prior to the beginning of a data transfer, data in the

TXPP

reg-

ister is automatically loaded into the Transmit Shift register. During a

DMA transmit operation, the data in

TXPP

is automatically loaded from

internal memory.

11-10

PPS

Parallel Port FIFO Status.

These read-only bits indicate

the status of the parallel port FIFO as follows: 00 =

RXPP/TXPP is empty

01 = RXPP/TXPP is partially full

11 = RXPP/TXPP is full

0

12

PPBHD

Parallel Port Buffer Hang Disable.

When cleared (= 0),

core stalls occur normally when the core attempts to write

to a full transmit buffer or read from an empty receive buf-

fer. Prevents a core hang when set (= 1). The old data pres-

ent in the receive buffer is read again if the core tries to

read it. If a write to the transmit buffer is performed, the

core will overwrite the current data in the buffer.

0

13

PPALEPL

Parallel Port ALE Polarity Level.

Asserts ALE active low if

set, (= 1) or active high if cleared, (= 0).

0

15–14

Reserved

0

16

PPDS

DMA Status.

Indicates that the internal DMA interface is

active if set, (= 1) or not active if cleared, (= 0).

0

17

PPBS

Parallel Port Bus Status.

Indicates that the external bus

interface is busy if set, (= 1) or available if cleared, (= 0).

The bus will be “busy” until one ALE cycle,

RD

cycle or

WR

cycle has taken place.

0

31–18

Reserved

0

Table A-33. Parallel Port Register (PPCTL) Bit Definitions (Cont’d)

Bit

Name

Definition

Default

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...