Chapter 5: IP Core Architecture

5–5

Transaction Layer

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

Interrupts

The Stratix V Hard IP for PCI Express offers three interrupt mechanisms:

■

Message Signaled Interrupts (MSI)— MSI uses the Transaction Layer's

request-acknowledge handshaking protocol to implement interrupts. The MSI

Capability structure is stored in the Configuration Space and is programmable

using Configuration Space accesses.

■

MSI-X—The Transaction Layer generates MSI-X messages which are single dword

memory writes. In contrast to the MSI capability structure, which contains all of

the control and status information for the interrupt vectors, the MSI-X Capability

structure points to an MSI-X table structure and MSI-X PBA structure which are

stored in memory.

■

Legacy interrupts—The

app_int_sts

input port controls legacy interrupt

generation. When

app_int_sts

is asserted, the Hard IP generates an

Assert_INT

<n>

message TLP.

For more detailed information about interrupts, refer to

.

PIPE

The PIPE interface implements the Intel-designed PIPE interface specification. You

can use this parallel interface to speed simulation; however, you cannot use the PIPE

interface in actual hardware. The Gen1 and Gen2 simulation models support pipe and

serial simulation. The Gen3 simulation model supports serial simulation only with

equalization bypassed.

Transaction Layer

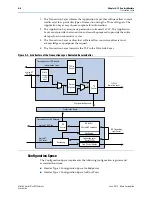

The Transaction Layer is located between the Application Layer and the Data Link

Layer. It generates and receives Transaction Layer Packets.

illustrates the

Transaction Layer. The Transaction Layer includes three sub-blocks: the TX datapath,

the Configuration Space, and the RX datapath, which are shown in

.

Tracing a transaction through the RX datapath includes the following steps:

1. The Transaction Layer receives a TLP from the Data Link Layer.

2. The Configuration Space determines whether the TLP is well formed and directs

the packet based on traffic class (TC).

3. TLPs are stored in a specific part of the RX buffer depending on the type of

transaction (posted, non-posted, and completion).

4. The TLP FIFO block stores the address of the buffered TLP.

5. The receive reordering block reorders the queue of TLPs as needed, fetches the

address of the highest priority TLP from the TLP FIFO block, and initiates the

transfer of the TLP to the Application Layer.

6. When ECRC generation and forwarding are enabled, the Transaction Layer

forwards the ECRC dword to the Application Layer.

Tracing a transaction through the TX datapath involves the following steps: