•

Texas Instruments Synchronous Serial Protocol (SSP)

on page 19-13

Serial Transfers

“National Semiconductor Microwire Protocol” describes the Microwire serial protocol in detail, including

timing diagrams and information about how data are structured in the transmit and receive FIFO buffers

before and after a serial transfer. The Microwire protocol operates in much the same way as the SPI protocol.

There is no decode of the control frame by the SPI slave device. †

Related Information

National Semiconductor Microwire Protocol

on page 19-14

Partner Connection Interfaces

The SPI can connect to any serial-master or serial-slave peripheral device using one of several interfaces.

Motorola SPI Protocol

The inactive state of the serial clock is low. The data frame can be 4 to 16 bits in length. †

Data transmission begins on the falling edge of the slave select signal. The first data bit is captured by the

master and slave peripherals on the first edge of the serial clock; therefore, valid data must be present on the

txd

and

rxd

lines prior to the first serial clock edge. †

The slave select signal takes effect only when used as slave SPI. For master SPI, the data transmission begins

as soon as the output enable signal is deasserted.

The following signals are illustrated in the timing diagrams in this section: †

•

sclk_out

—serial clock from SPI master †

•

sclk_in

—serial clock from SPI slave †

•

ss_0_n

—slave select signal from SPI master †

•

ss_oe_n

—output enable for the SPI master or slave †

•

txd

—transmit data line for the SPI master or slave †

•

rxd

—receive data line for the SPI master or slave †

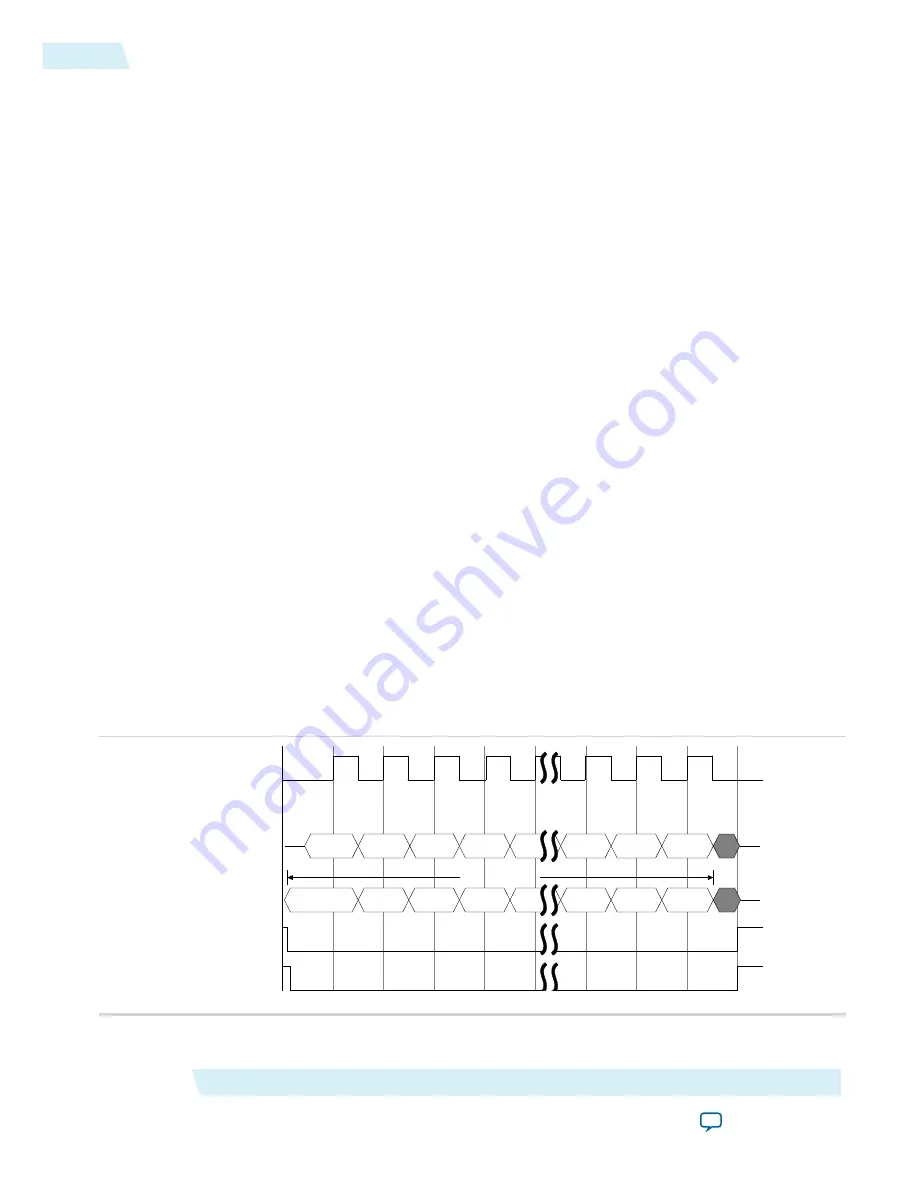

Figure 19-6: SPI Serial Format

4 - 16 bits

B

S

L

B

S

M

B

S

L

B

S

M

sclk_out/in 0

txd

rxd

ss_0_n/ss_in_n

ss_oe_n

SPI Controller

Altera Corporation

cv_54019

Serial Transfers

19-12

2013.12.30