ADM-PCIE-9V5 User Manual

3.3 PCI Express

The ADM-PCIE-9V5 is capable of PCIe Gen 3 with 8 lanes. The FPGA drives these lanes directly using the

Integrated PCI Express block from Xilinx. Negotiation of PCIe link speed and number of lanes used is generally

automatic and does not require user intervention.

PCI Express reset (PERST#) connected to the FPGA through a buffer. See

signal

PERST0_1V8_L.

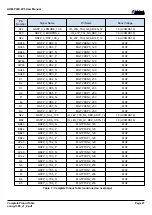

The other pin assignments for the high speed lanes are provided in the pinout attached to the

The PCI Express specification requires that all add-in cards be ready for enumeration within 120ms after power

is valid (100ms after power is valid + 20ms after PERST is released). The ADM-PCIE-9V5 does meet this

requirement when configured from a tandem bitstream with the proper SPI constraints detailed in the section:

Configuration From Flash Memory. For more details on tandem configuration, see Xilinx xapp 1179.

Note:

Different motherboards/backplanes will benefit from different RX equalization schemes within the PCIe IP core

provided by Xilinx. Alpha Data recommends using the following setting if a user experiences link errors or

training issues with their system: within the IP core generator, change the mode to "Advanced" and open the

"GT Settings" tab, change the "form factor driven insertion loss adjustment" from "Add-in Card" to

"Chip-to-Chip" (See Xilinx PG195, PG213, and PG239 for more details).

Page 13

Functional Description

ad-ug-1385_v1_0.pdf