MC96FM204/FM214

98

April 7, 2016 Ver. 1.8

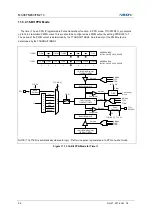

11.5.5 Block Diagram

T1MS[1:0]

T1POL

Reload

A Match

T1CC

T1EN

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/64

fx/512

fx/2048

fx/8

fx/1

Comparator

16-bit Counter

T1CNTH/T1CNTL

16-bit B Data Register

T1BDRH/T1BDRL

Clear

B Match

Edge

Detector

T1ECE

EC1

Buffer Register B

Comparator

16-bit A Data Register

T1ADRH/T1ADRL

T1IFR

INT_ACK

Clear

To interrupt

block

A Match

Buffer Register A

Reload

Pulse

Generator

T1O/

PWM1O

R

EINT11

T1CNTR

T1EN

3

T1CK[2:0]

Clear

EIPOLB[1:0]

FLAG11

(EIFLAG.4)

INT_ACK

Clear

To interrupt

block

2

2

T1MS[1:0]

2

A Match

T1CC

T1EN

A Match

T1CC

T1EN

Figure 11.15 16-Bit Timer 1 Block Diagram

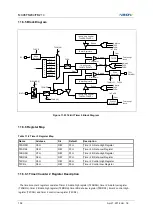

11.5.6 Register Map

Table 11-6 Timer 2 Register Map

Name

Address

Dir

Default

Description

T1ADRH

BDH

R/W

FFH

Timer 1 A Data High Register

T1ADRL

BCH

R/W

FFH

Timer 1 A Data Low Register

T1BDRH

BFH

R/W

FFH

Timer 1 B Data High Register

T1BDRL

BEH

R/W

FFH

Timer 1 B Data Low Register

T1CRH

BBH

R/W

00H

Timer 1 Control High Register

T1CRL

BAH

R/W

00H

Timer 1 Control Low Register

11.5.6.1 Timer/Counter 1 Register Description

The timer/counter 1 register consists of timer 1 A data high register (T1ADRH), timer 1 A data low register

(T1ADRL), timer 1 B data high register (T1BDRH), timer 1 B data low register (T1BDRL), timer 1 control High

register (T1CRH) and timer 1 control low register (T1CRL).

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...