14.3.5

Settings

PID-6513-SETTINGS v4

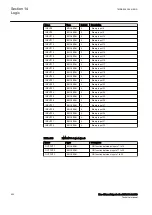

Table 259:

TMAGAPC Group settings (basic)

Name

Values (Range)

Unit

Step

Default

Description

Operation

Off

On

-

-

Off

Operation Off / On

PulseTime

0.050 - 60.000

s

0.001

0.150

Output pulse time

OnDelay

0.000 - 60.000

s

0.001

0.000

Output on delay time

OffDelay

0.000 - 60.000

s

0.001

0.000

Output off delay time

ModeOutput1

Steady

Pulsed

-

-

Steady

Mode for output ,1 steady or pulsed

ModeOutput2

Steady

Pulsed

-

-

Steady

Mode for output 2, steady or pulsed

ModeOutput3

Steady

Pulsed

-

-

Steady

Mode for output 3, steady or pulsed

14.3.6

Operation principle

SEMOD52537-5 v8

The trip matrix logic (TMAGAPC) block is provided with 32 input signals and 3

output signals. The function block incorporates internal logic OR gates in order to

provide grouping of connected input signals to the three output signals from the

function block.

Internal built-in OR logic is made in accordance with the following three rules:

1. when any one of first 16 inputs signals (INPUT1 to INPUT16) has logical

value 1 the first output signal (OUTPUT1) will get logical value 1.

2. when any one of second 16 inputs signals (INPUT17 to INPUT32) has logical

value 1 the second output signal (OUTPUT2) will get logical value 1.

3. when any one of all 32 input signals (INPUT1 to INPUT32) has logical value

1 the third output signal (OUTPUT3) will get logical value 1.

By use of the settings

ModeOutput1

,

ModeOutput2

,

ModeOutput3

,

PulseTime

,

OnDelay

and

OffDelay

the behavior of each output can be customized. The

OnDelay

is always active and will delay the input to output transition by the set

time. The

ModeOutput

for respective output decides whether the output shall be

steady with an drop-off delay as set by

OffDelay

or if it shall give a pulse with

duration set by

PulseTime

. Note that for pulsed operation and that the inputs are

connected in an OR-function, a new pulse will only be given on the output if all

related inputs are reset and then one is activated again. For steady operation the

OffDelay

will start when all related inputs have reset. Detailed logical diagram is

1MRK 505 394-UEN A

Section 14

Logic

Line differential protection RED650 2.2 IEC

451

Technical manual

Summary of Contents for RED650

Page 1: ...RELION 650 SERIES Line differential protection RED650 Version 2 2 Technical manual...

Page 2: ......

Page 36: ...30...

Page 46: ...40...

Page 232: ...226...

Page 272: ...266...

Page 288: ...282...

Page 306: ...300...

Page 406: ...400...

Page 436: ...430...

Page 502: ...496...

Page 614: ...608...

Page 628: ...622...

Page 644: ...638...

Page 760: ...754...

Page 778: ...772...

Page 814: ...808...

Page 870: ...864...

Page 874: ...868...

Page 924: ...918...

Page 925: ...919...