Publication No. PPC11A-HRM/1

Specifications 127

A •

Specifications

A.1 Technical Specification

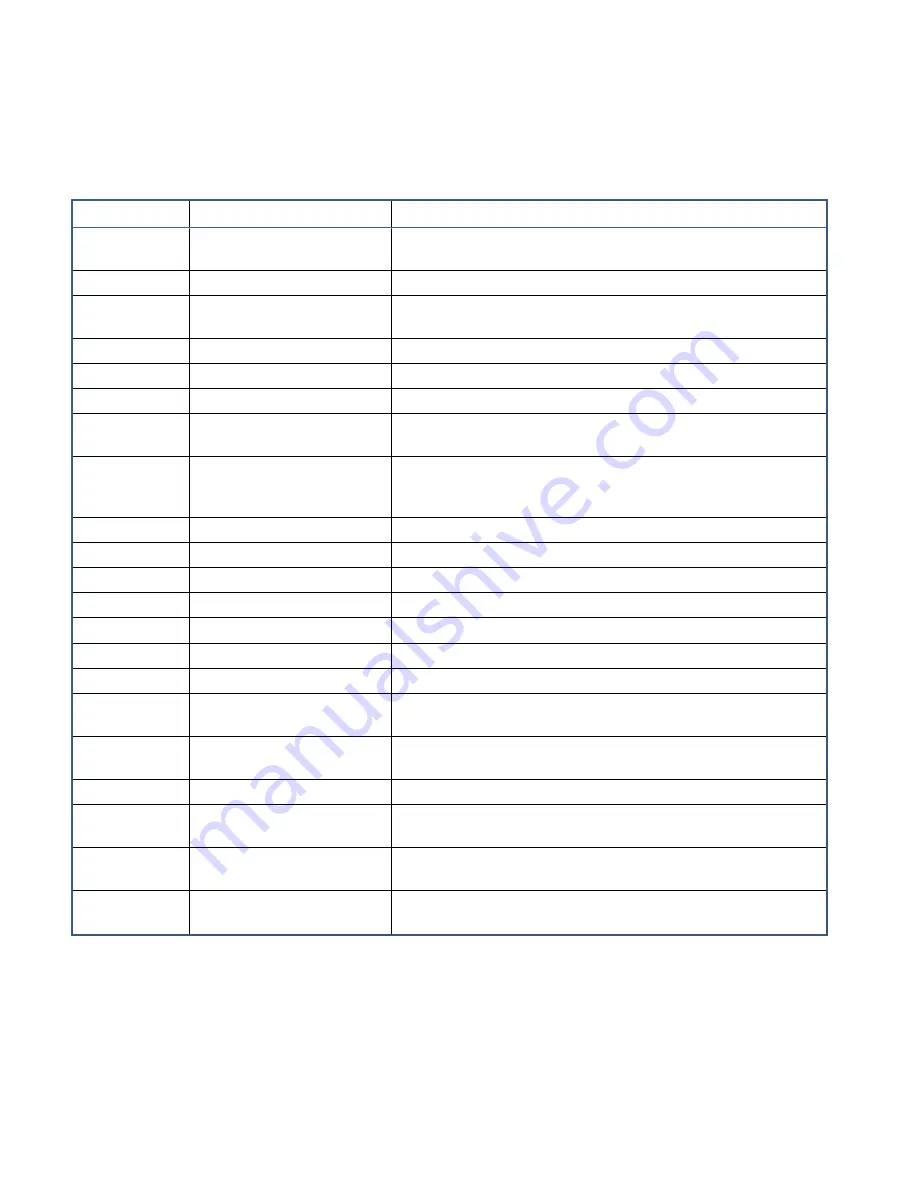

Table A-1 Technical Data

Features

Details

Comments

Processor

NXP T2081 or T1042 processor

Contains four PowerPC processing cores: e6500 (T2081) @ 1.8 GHz, e5500

(T1042) @ 1.4 GHz

RAM

8 GB DDR3L SDRAM with ECC

Dual memory controllers running at up to 650 MHz

ROM

512 MB NOR Flash memory

8 MB allocated to Boot Flash and the rest to User Flash. Advanced sector

protection features

NOVRAM

512 KB

Non-volatile storage for data that must not be lost when power is removed

Solid State Drive

32 GB (optional)

SATA SSD

Infrastructure

PCIe

High bandwidth serial-interconnect. Non-blocking switch architecture

Ethernet ports

Two 10/100/1000BASE-T and

Two optional 10/100/1000BASE-T

Ethernet 3 and Ethernet 4 are a build option over GPIO

Serial ports

Two RS232/RS422 debug

Four RS232/422/485

Synchronous/Asynchronous

Processor provides COM1 & COM2 debug ports.

FPGA provides COM3 to COM6

USB2.0

Up to two ports

To the backplane

SATA

Two backplane channels

SATA-300

Discrete Digital I/O

Up to 19-bits, TTL-compatible

Able to generate edge- or level-triggered interrupts

VME

VME64 support to P1/P2

Fully backward compatible

MIL-STD-1553

Up to two ports

Dual redundant, sidebands optional

Video

VGA or DVI

DVI with T1042 processor only

PMC/XMC sites

Two PMC/XMC Sites

64-bit PCI-X interface at up to 133 MHz. x4 PCIe interface

DMA controllers

Twelve

Eight engines available in the processor for efficiently moving large blocks of

data. Four further engines available in the PCIe switches

Timers

Eight 31-bit timers

Provided by the processor. Programmable frequency with up to 15 ns

resolution. Ability to cascade to form larger timers

Watchdog timer

Two 32-bit timers

Programmable interrupt and reset thresholds

Real-Time Clock

Time of Day/Calendar

1 second resolution. Standby power may be connected from the VBAT pin to

maintain data during power down

ETI

Quarter second resolution

Logs the total accumulated time the PPC11A has been powered, and the

number of power cycles

JTAG Interface

VME backplane JTAG to VME

Bridge and mezzanine sites

JTAG via TAC for processor debugger and boundary scan purposes