Overview

The LC78626KE is a monolithic compact disk player

signal processing and servo control CMOS IC equipped

with an internal anti-shock control function. Designed for

total functionality including support for EFM-PLL, and

one-bit D/A converter, and containing analog low-pass

filter, the LC78626KE provides optimal cost-performance

for low-end CD players that provide anti-shock systems

by eliminating as many unnecessary features as possible.

The basic functions provided by this IC include

modulation of the EFM signal from the optical pick-up,

deinterleaving, detection and correction of signal errors,

prevention of a maximum of approximately 38 seconds of

skipping, signal processing such as digital filtering (which

is useful in reducing the cost of the player), and processing

of a variety of servo-related commands from the

microprocessor. The LC78626KE is an improved version

of the LC78626E. It provides 8

×

oversampling digital

filters and supports up to 16M of DRAM.

Functions

• When an HF signal is input, it is sliced to precise levels

and converted to an EFM signal. The phase is compared

with the internal VCO and a PLL clock is reproduced at

an average frequency of 4.3218 MHz.

• Precise timing for a variety of required internal timing

needs (including the generation of the reference clock) is

produced by the attachment of an external 16.9344 MHz

crystal oscillator.

• The speed of revolution of the disk motor is controlled

by the frame phase difference signal generated by the

playback clock and the reference clock.

• The frame synchronizing signal is detected, stored, and

interpolated to insure stable data read back.

• The EFM signal is demodulated and converted to 8-bit

symbolic data.

• The demodulated EFM signal is divided into subcodes

and output to the external microprocessor. (Three

general I/O ports are shared [exclusively] for this

purpose.)

• After the subcode Q signal passes the CRC check, it is

output to the microprocessor through a serial

transmission (LSB first).

• The demodulated EFM signal is buffered in the internal

RAM, which is able to absorb ±4 frame’s worth of jitter

resulting from variations in the disk rotation speed.

• The demodulated EFM signal is unscrambled to a

specific sequence, and deinterleaving is performed.

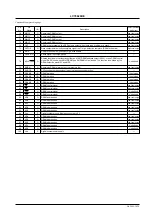

Package Dimensions

unit: mm

3151-QFP100E

21.6

0.8

3.0max

1.6

17.2

0.825

1

30

31

50

51

80

81

1.6

0.575

0.575

0.15

2.7

15.6

0.3

20.0

23.2

14.0

0.65

0.825

100

0.8

0.65

0.1

CMOS IC

21099RM(OT) No. 5995-1/34

SANYO: QFP100E (QIP100E)

[LC78626KE]

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-0005 JAPAN

DSP for Compact Disk Players

LC78626KE

Ordering number : EN5995

Continued on next page.

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft’s

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.